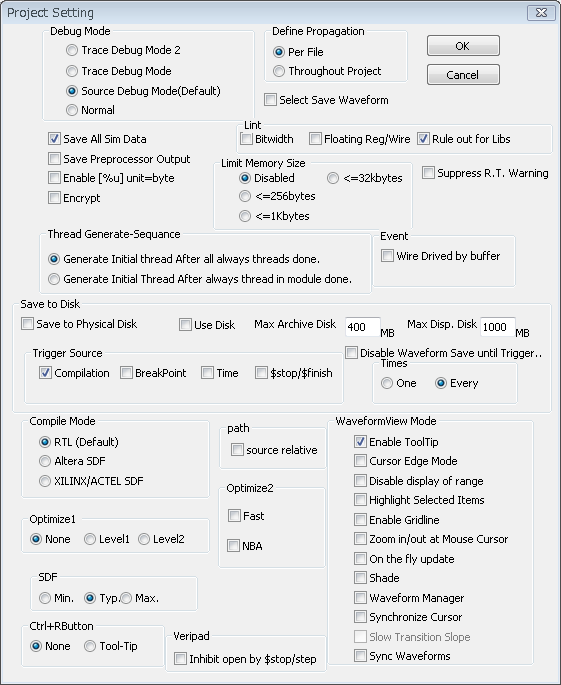

Note

- To Enable breakpoint, "source debug mode" or higher should be

checked

- In Altera Gate simulation "Altera SDF" to be checked otherwise

"RTL" to be checked..

- To view waveform data, "Save All Sim Data" to be checked

- Optimize Leve2 is recommended. This is net structure optimization switch,

however if your design is like gate level or has many instances(Ex >10000),

Use Level1/None instead.

- NBA option is interim. This makes for example,Ignore #1 in such as a<=#1

b; statement on always process. This is RTL simulation use only.Do not

set on gate simulation. Aggressive scheduling change will be applied in

future version.

- If you set "Throughout Project, DEFINES propagate

throughout the Project. It is noted order of files in the

project should be taken care of. See sample project "define_propagation.vtakprj"

in samples folder. Be care of sequence of the files. Basically Veritak

processes in order of the files, however there is a exception. It is noted

Library files are processed at last in any position of library statement

in the project.

- Each library directory file should have either the same name as a UDP or

a top-level

module it contains, or that name plus an extension,".v" or ".V".It should be noted file name is case sensitive. Library compilation is always source level.

If you don't like such a rule (same file name to module name), use Re-Compile button to compile all files in the library folder.

- Source_relative option is useful per following case.. For example,

consider readmemh(mem, "./mem/hoge.mem"); Folder where Veritak

Project file exists is default base folder. If project file and source

files are in the same folder, there is no problem. However if they are

not in the same folder, it may be problem. This option enables certain

relative path to source file in system task such as $fopen/$readmemh.

- Refer to save/restore for Save to Disk

- Refer to Use WaveformViewManger

- Refer to Shade

- If "Enable [%u] unit=byte" is checked, $write("%u",hoo)

is written in the unit of 8bit(byte). This setting is default before version

3.24A. If the check is Off, $write("%u",hoo) is written in the

unit of 32bits(Verilog-2001 LRM). This is default from the Version 3.24A.

- "wire driven by buffer" option slightly changes default thread sequence.This may be useful under race condition,. comparing the result with other simulator's.

- Refer to Select Instances for waveform view

- To suppress run-time warning, check Suprees R.T. warning

- Checking Rule out for Libs disables LINT for library files..

Fastest Setting (No Save Data, No Debug,)

- Fast Switch is On

- Debug Mode Normal to be checked

- Save All Sim Data off

- Optimize Level2 to be checked

- NBA option to be checked

To enable these setting, re-compilation will be required.

<Use

Use Disk for long vector view>

ArchiveDisk is maximum value for saving all the data as compressed archive.

DispDisk is maximum value for extracting data for display. If

Use Disk is set , these data are taken from Disk not memory, mapping 64bit address

space, which will resolve 32bit address space problem if you are using

NTFS format. It is noted maximum capacity is up to 4GB if you are

using FAT32.

Set enough value to hold the data. Status-bar shows progress of each data,so,

you can imagine entire data amount by

small examination.

Ex.

Opencores PCI required 7.5GB ArchiveDisk and 3GB DispDisk for 200

selected signals for entire simulation.

Opencores Divider required 1.3GB ArchiveDisk and 1.4GB DispDisk.

for entire simulation.

It is recommended you use

|+| for magnifying the term. Please note you will get slower response if you

look wider area..

As of Version 3.09, veritak does not have a method to see saved

view as stand-alone yet.