RTL Project

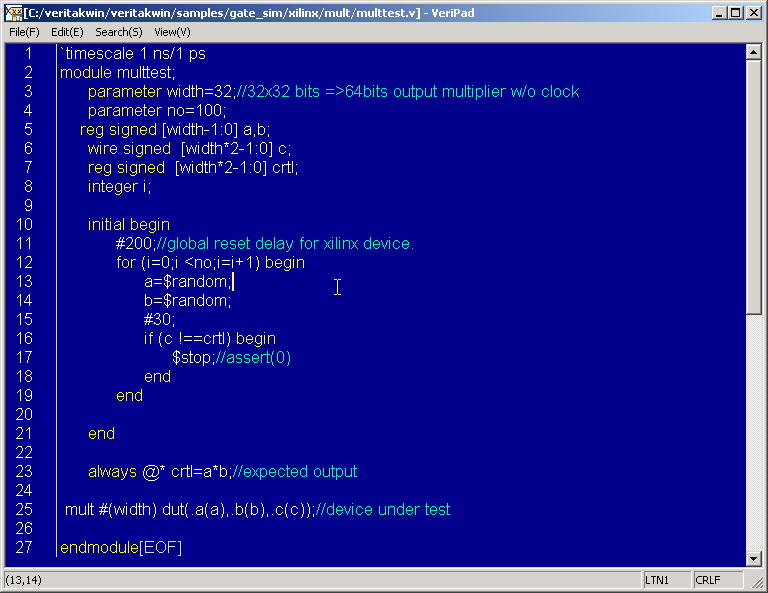

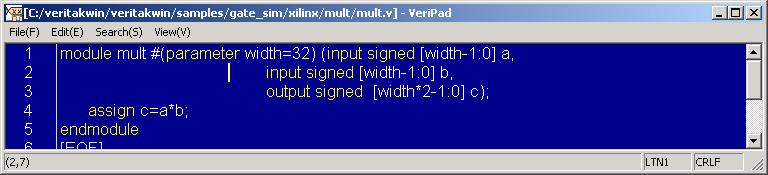

Let's design simple 32x32bits multiplier.

Load Project "RTL_mult_test.vtakprj", and press Go button.

Test bench source is as below.

Here is simple source for signed multiplier.

Synthesis

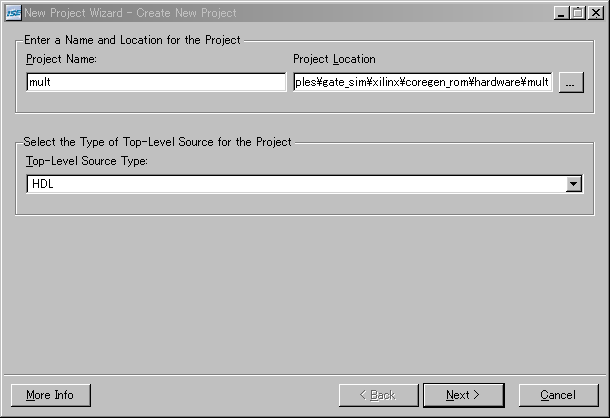

Let's make a Xilinx project for our multiplier.

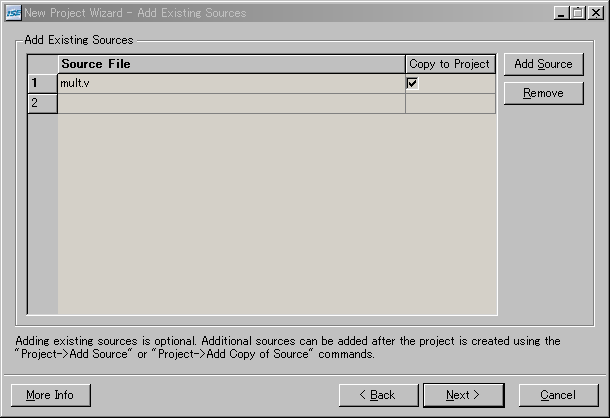

Add Source our "mult.v"

Veritak Gate Simulation Project

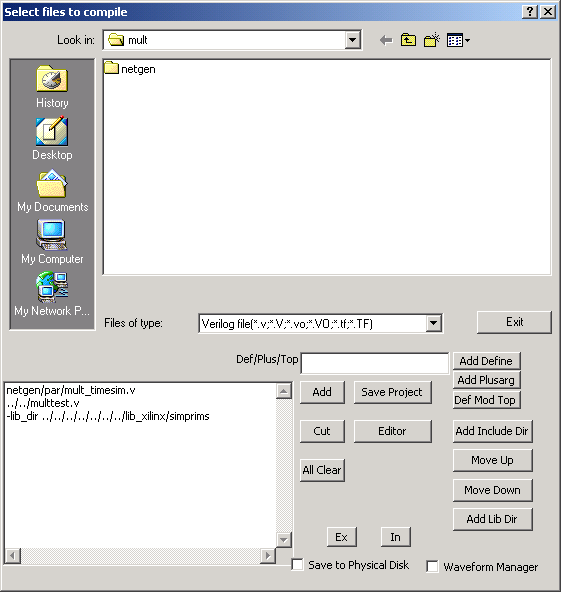

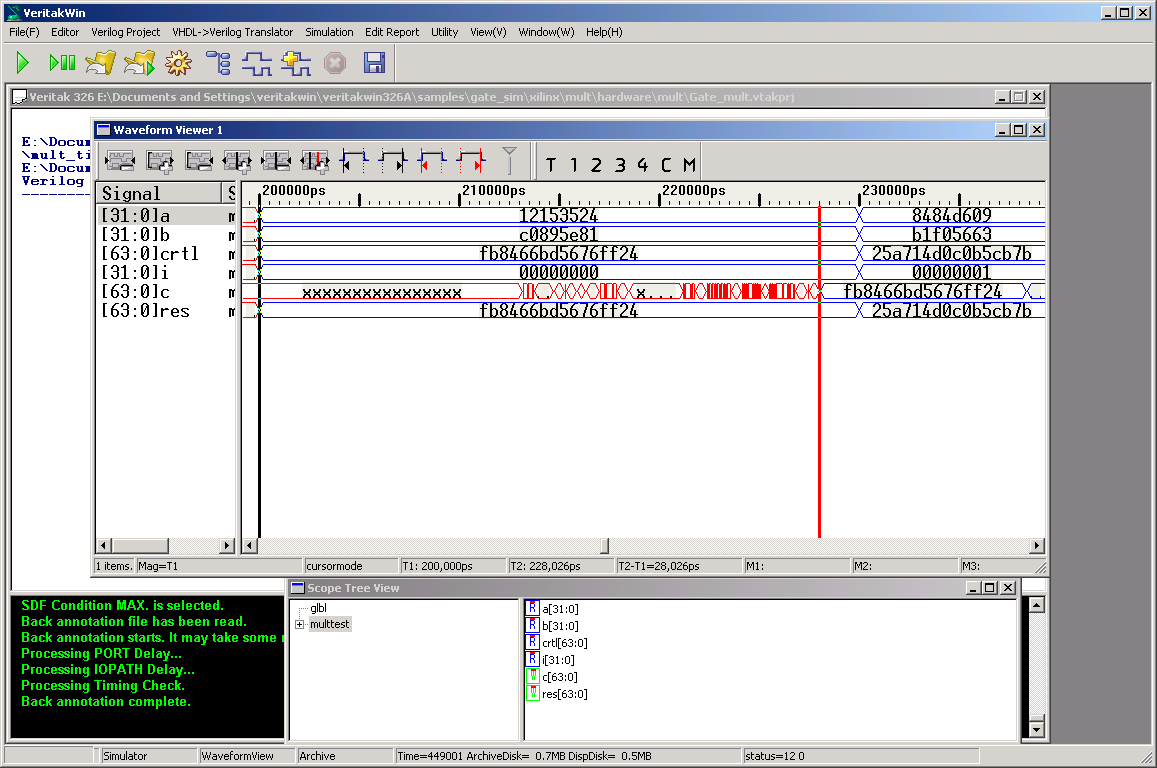

Let's view the veritak project for gate simulation.

Gate simulation project must be above "netgen" ( Xilinx tool

generates "netgen" folder). This is necessary because generated

net list file **timesim.v reads sdf file according to specified path.

Fig below shows veritak project in mult folder.Open the project (Gate_mult.vtakprj)

by the menu Verilog Project ->Open Verilog Project

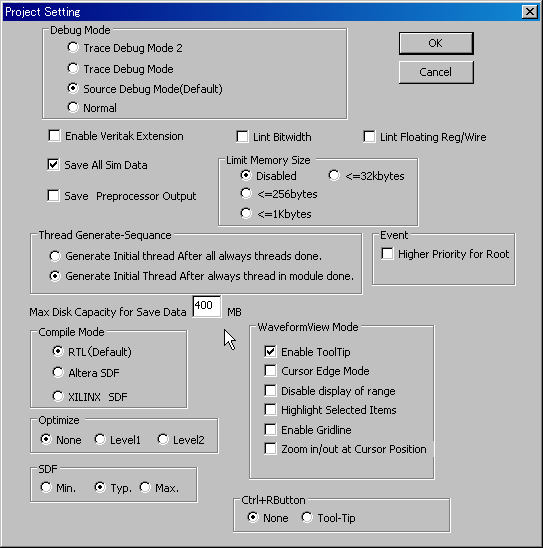

You can select Min/Typ/Max for SDF delay in Project Setting Dialog.. However

nothing will be changed as for Altera/Xilinx because the same values are

generated in SDF of Altera/Xilinx.

In compile mode, Use Xilinx SDF for Xilinx Gate Simulation.

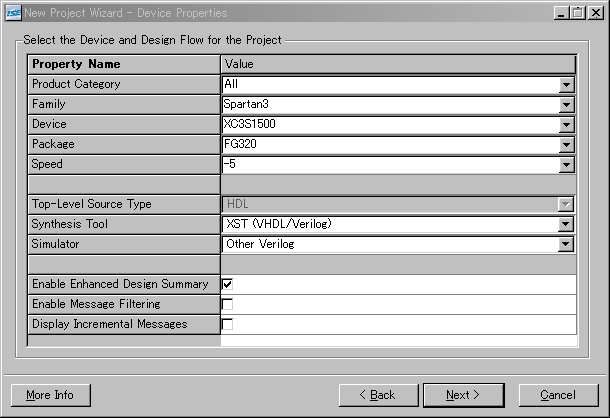

Family/Device is as you like..

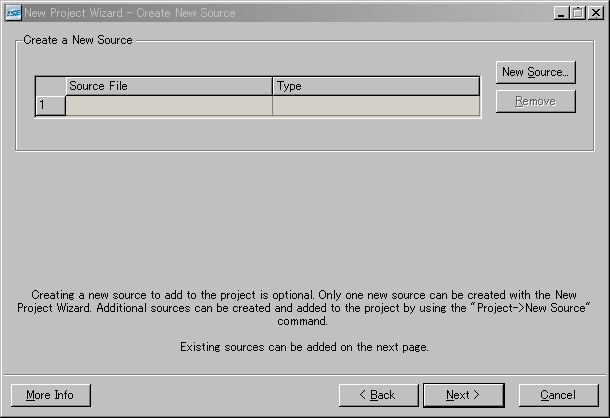

Nothing to be add in this time.

That's all for settings of the project

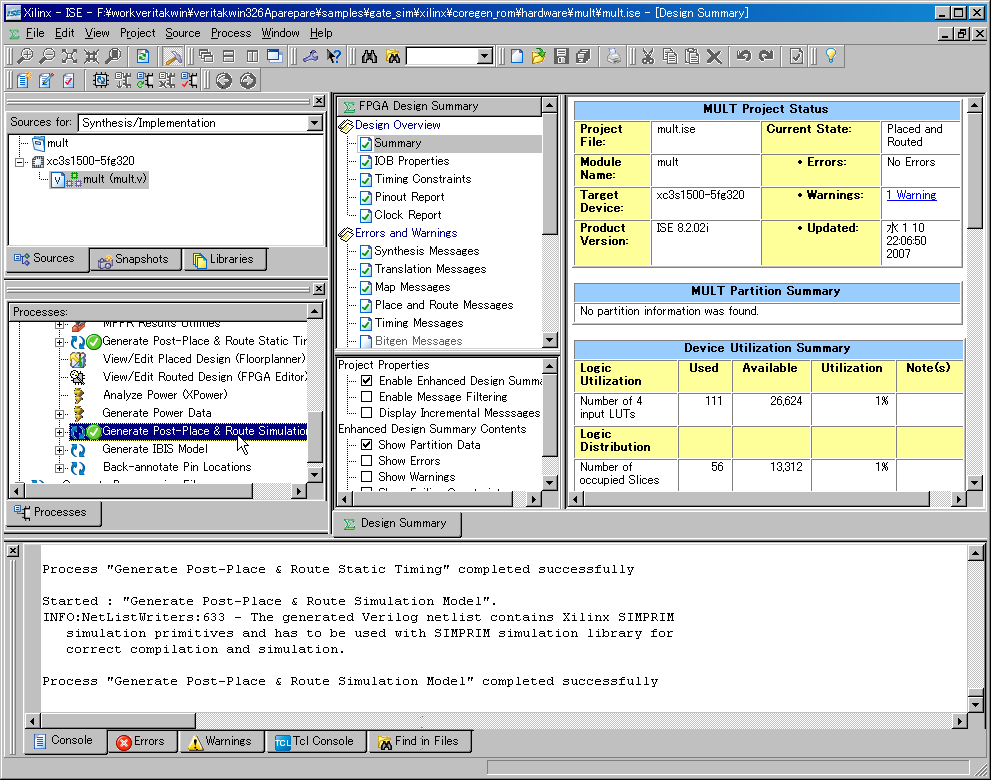

Run "Generate post-place & route simulation model" as below.

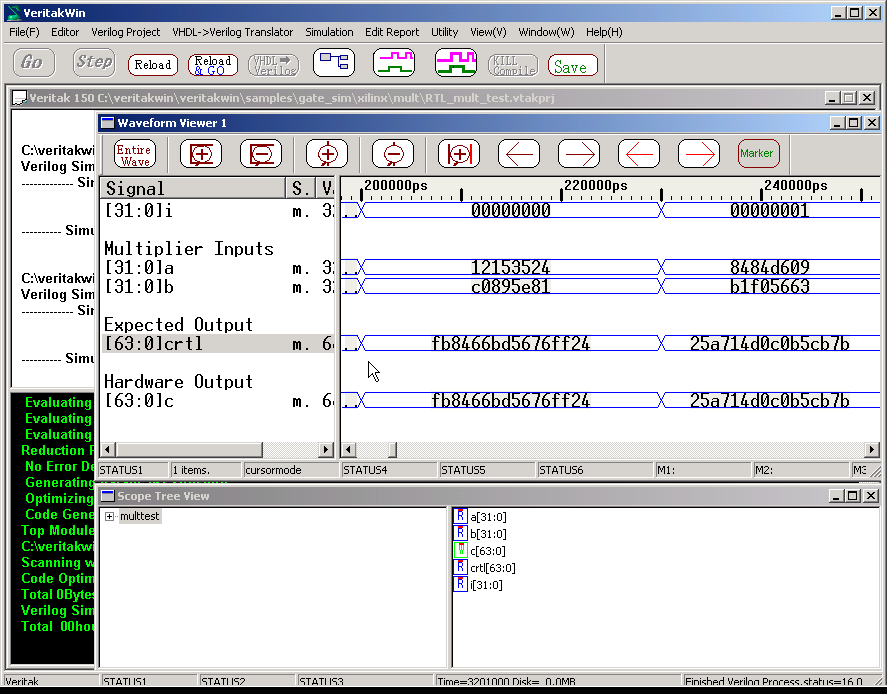

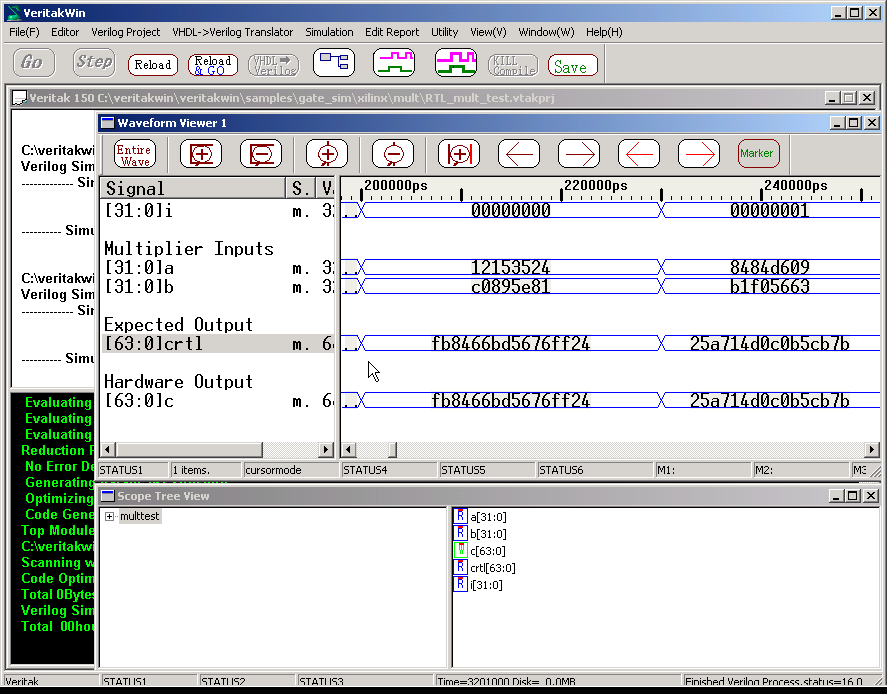

You can observe 28.026ns delay for RTL to Gate Simulation as a result of 12153524*c0895e81