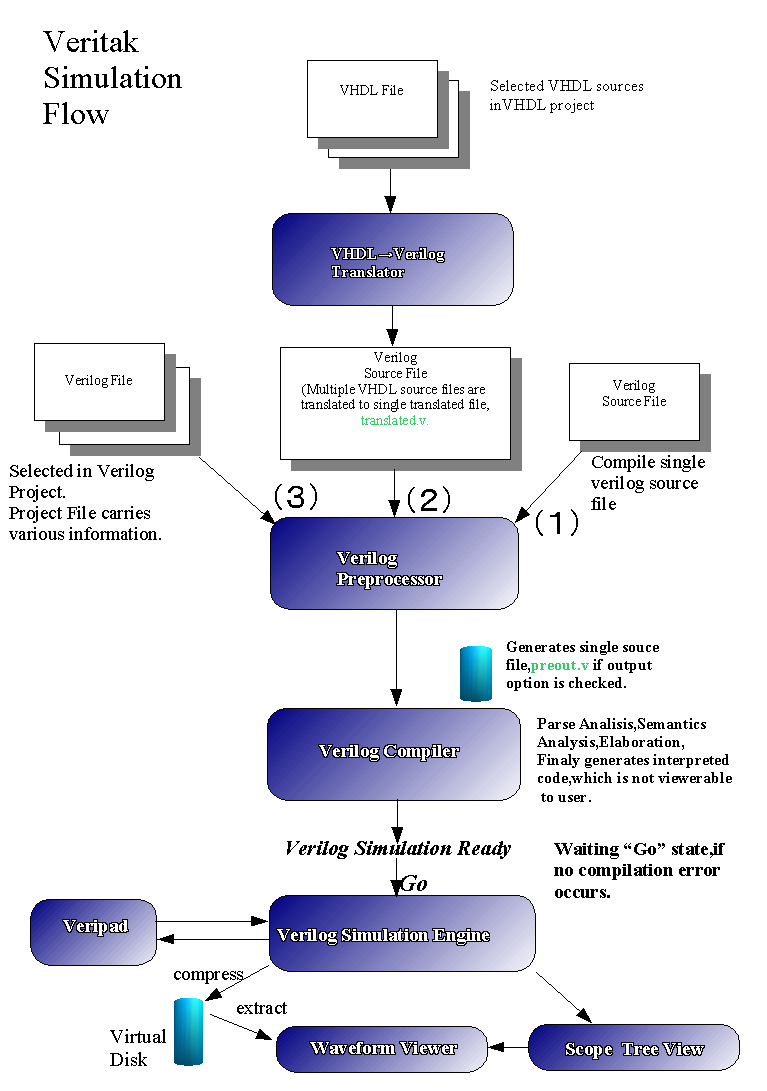

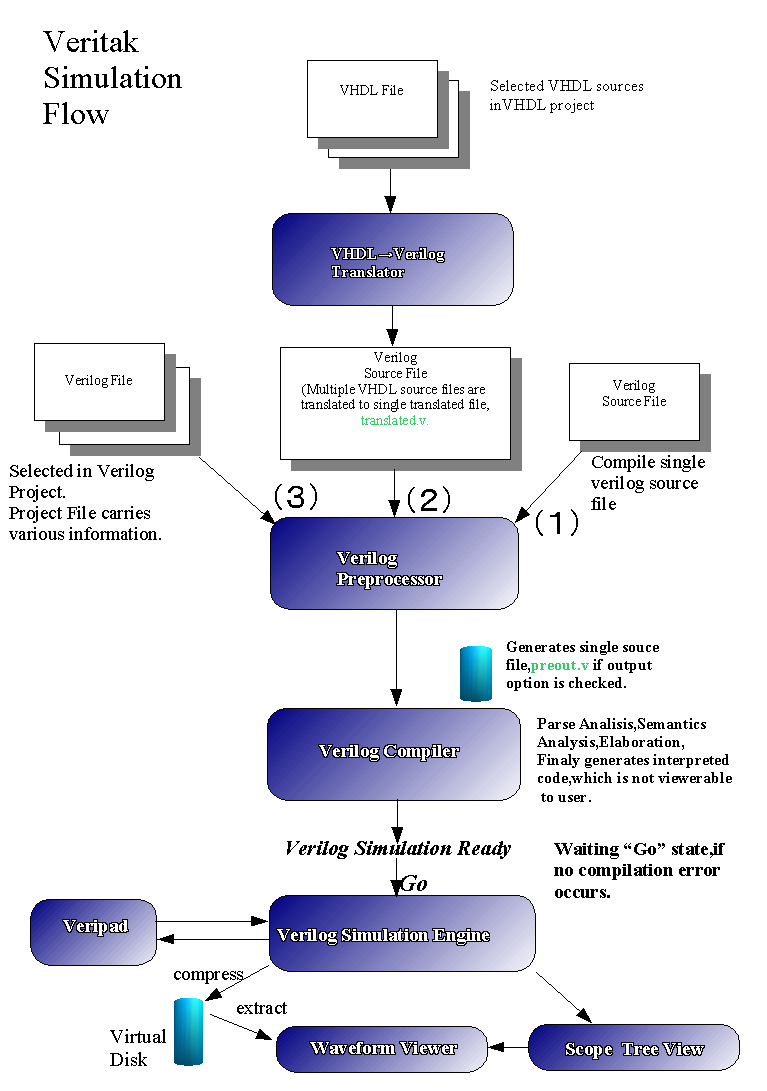

Figure below shows internal structure of Veritak.

Veritak consists of following programs

- Pre-Pre processing

- Preprocessing (prepro.exe)

- Compiler(veritak02.exe)

- Simulation Engine(Veritak02.exe)

- GUI Main Program (VeritakWin.exe)

- VHDL to Verilog Translator (show.exe)

- Dlls

If the project option "Define Propagation ->throughout Project

" is set,

a single file of "prepre_processed.v " is generated before preprocessing.

In Preprocess stage `define, `define macro, `include are processed.

Even in case of multiple source files, preprocessor generates single file (preout.v)

finally if project option is enabled.

In compile stage, parse analysis, semantics analysis are performed,

and final flattened instances are generated (this is called elaboration).

Instances are divided two parts, net-object and procedural interpreter

code. Net-object behaviors like real circuit component, and procedural

interpreter code consist of virtual CPU code.

After compilation finished, simulation engine waits

Go button pressed.

Third Stage is execution stage. GUI program(VeritakWin.exe) and simulation

engine shares virtual file. GUI compresses and decompress the data in appropriate

timing.