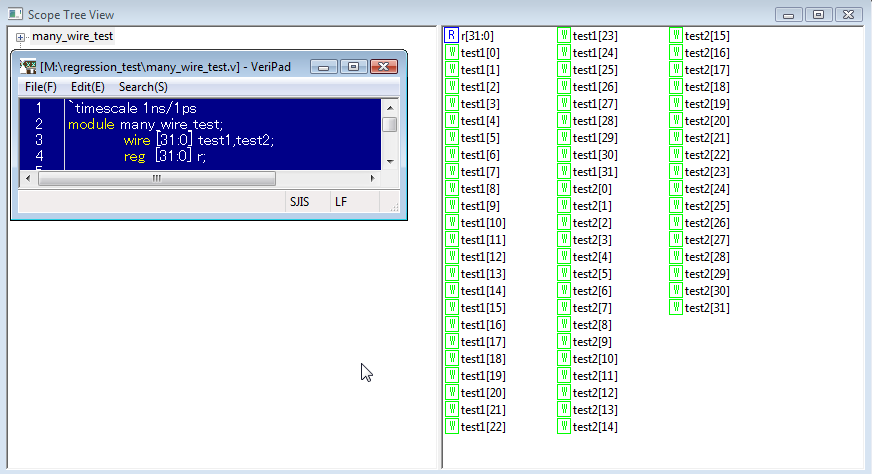

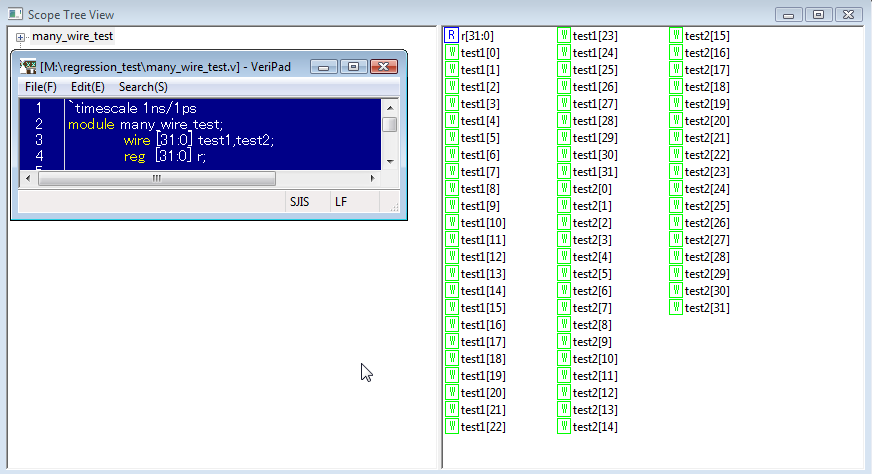

A sample below is ModelSim(TM) generated VCD. It is noted wire buses are expanded as each bit.

Sometimes this is frustrating for editing the signals on waveformview.

2.4.1.3 Automatic Grouping

A sample below is ModelSim(TM) generated VCD. It is noted wire buses are

expanded as each bit.

Sometimes this is frustrating for editing the signals on waveformview.

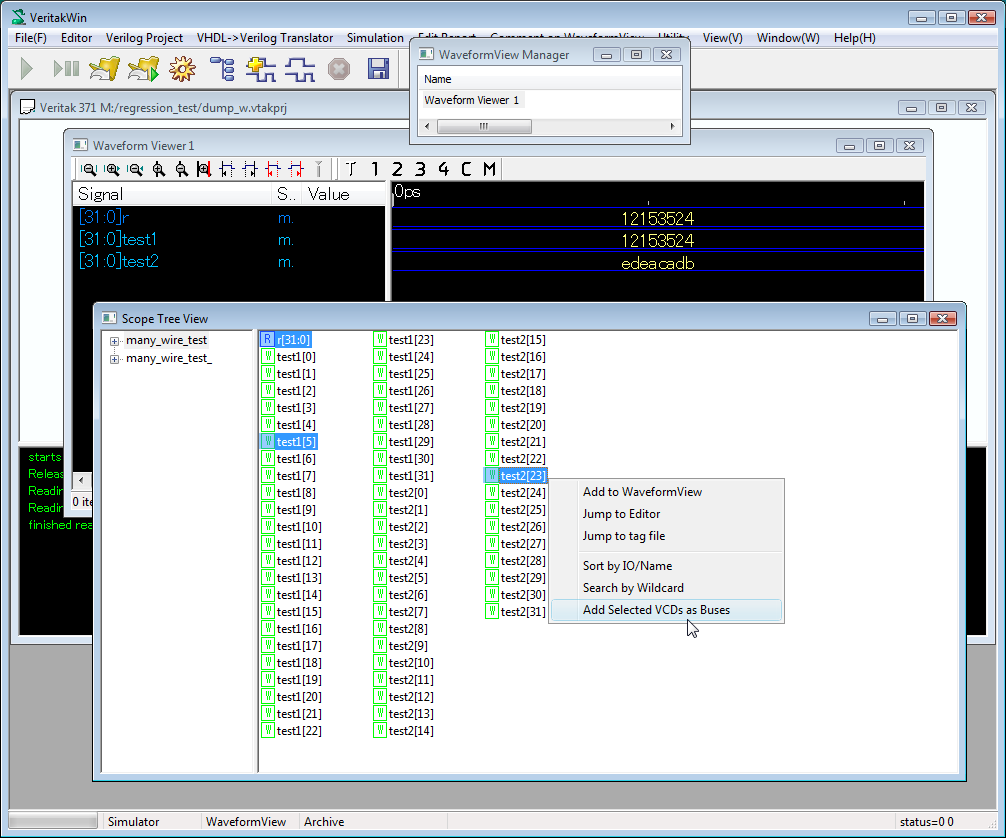

If you would like to view those signals as bus,Add selected signals as buses is useful as below.

(1bit selection is fully enough to make a bus.)

You can do it in another way.

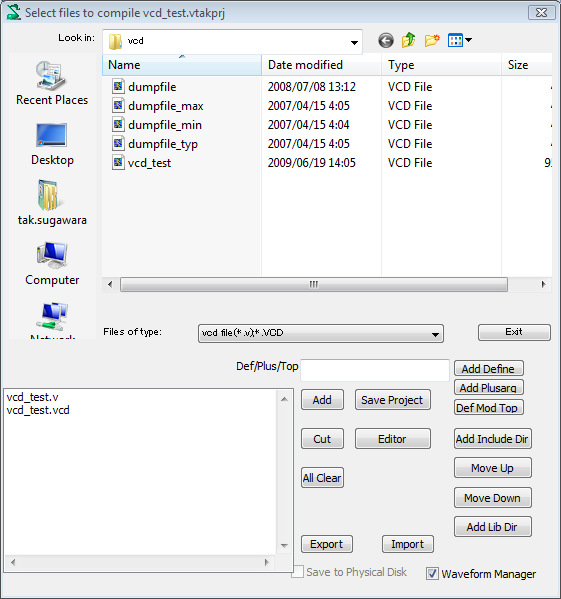

2.4.1.4 Display VCD and Veritak's waveform on same waveformview

Define vcd file in the project the same way.

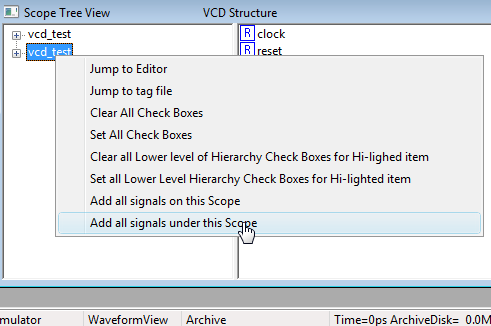

VCD Structure is displayed in title bar if the node is vcd.

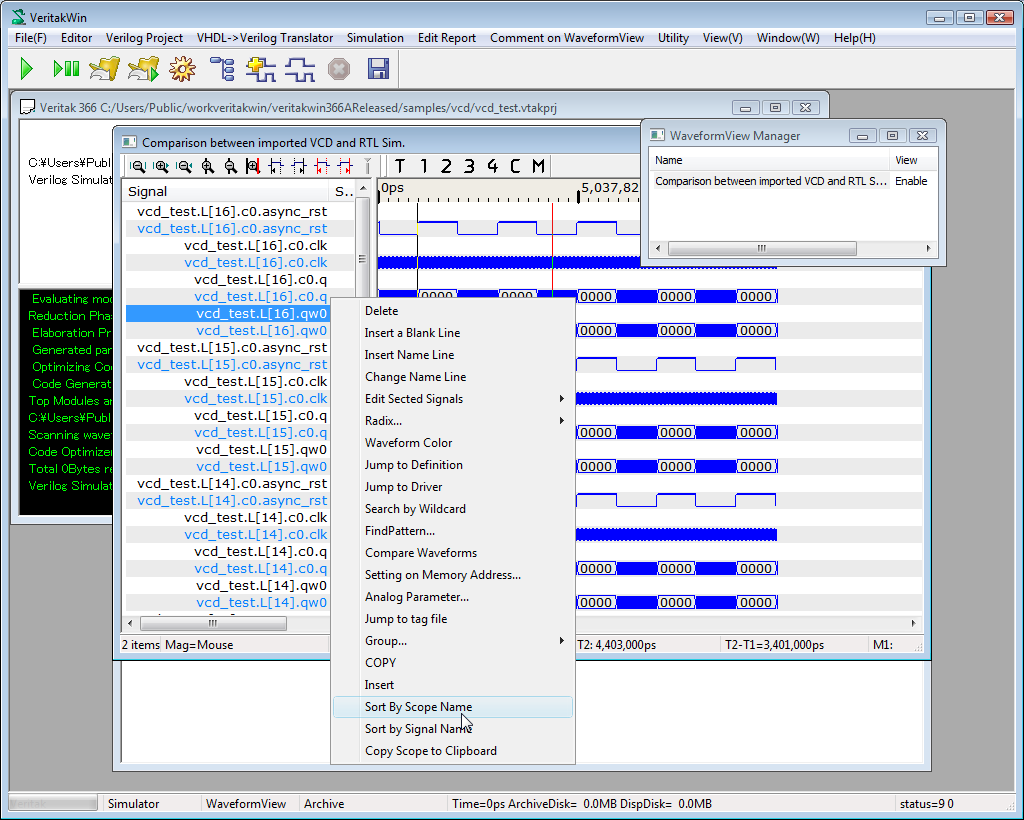

Sort By Scope will make easier to view between VCD and RTL sim.

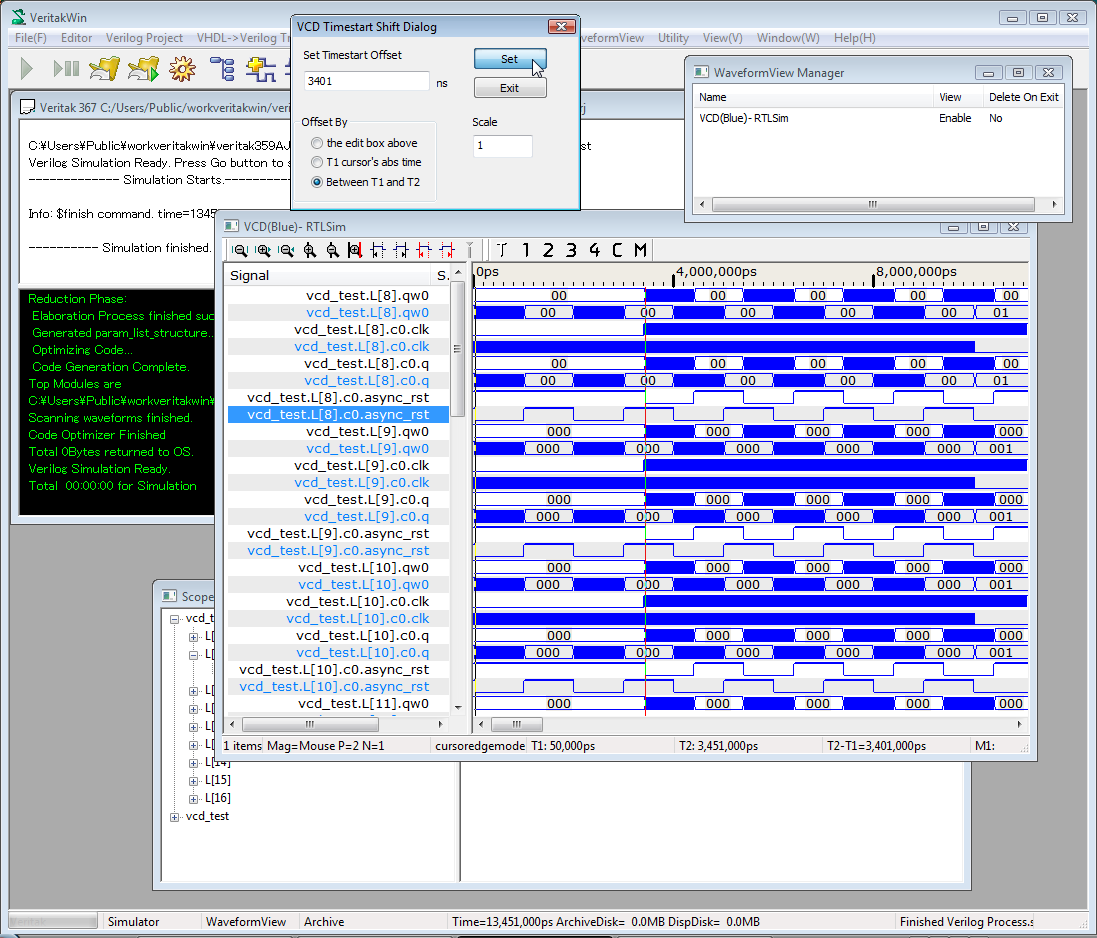

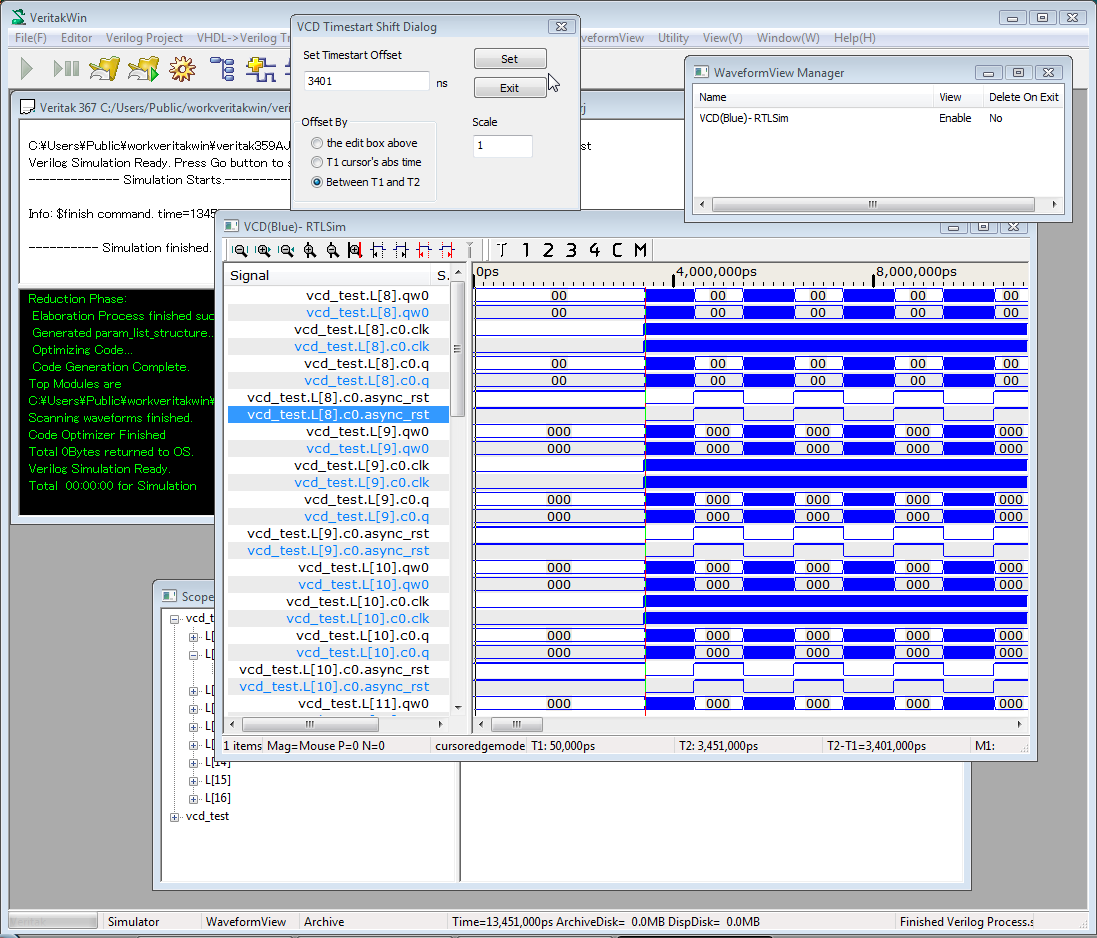

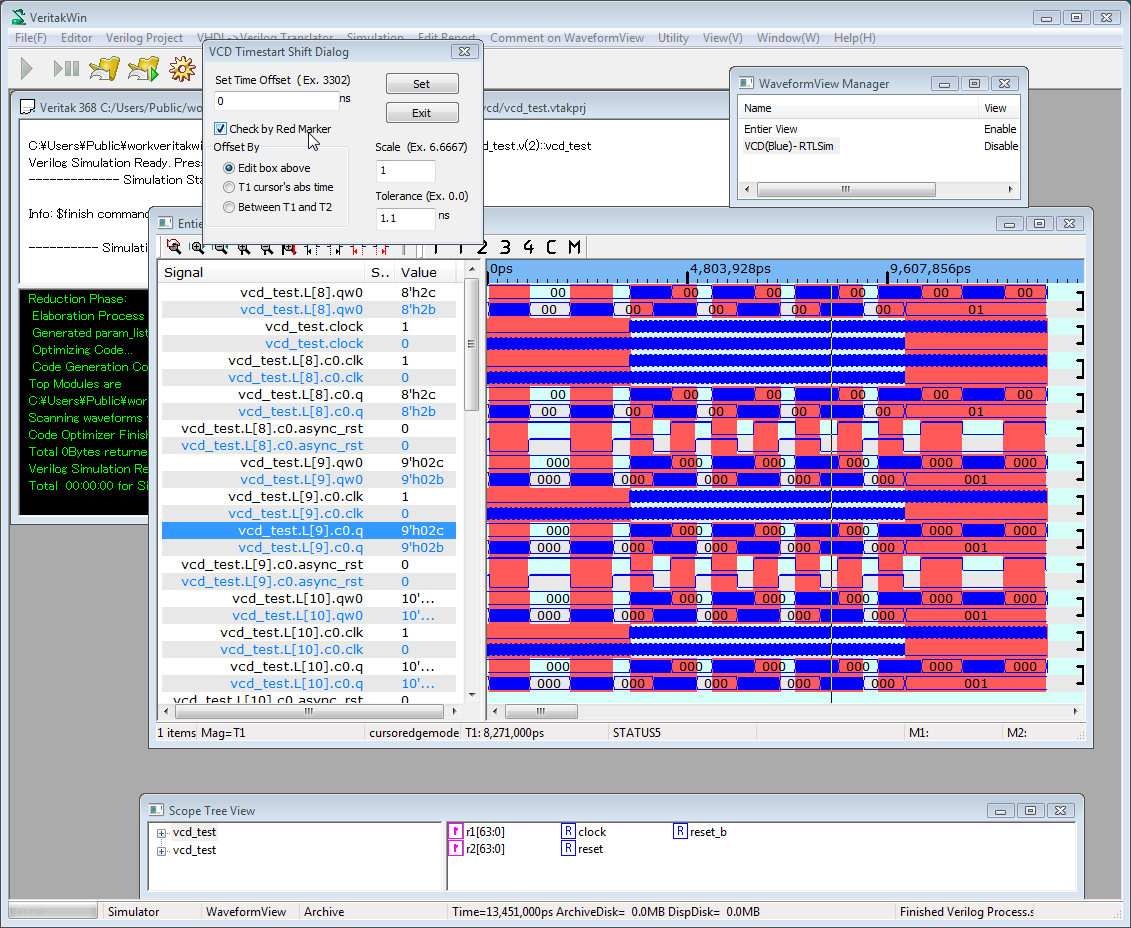

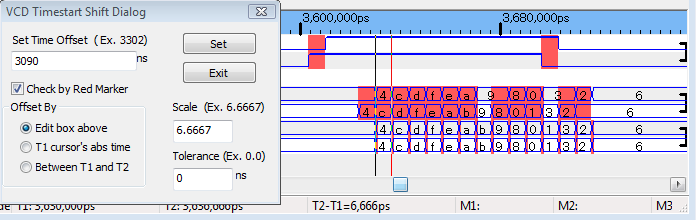

2.4.1.5 Shift VCD waveform

You'll see the dialog below by

Menu->Utility -> Add VCD Starttime Offset

You can set value by 3 alternative ways.

In this tutorial, we use difference between T1 and T2 cursor.

TIPS:

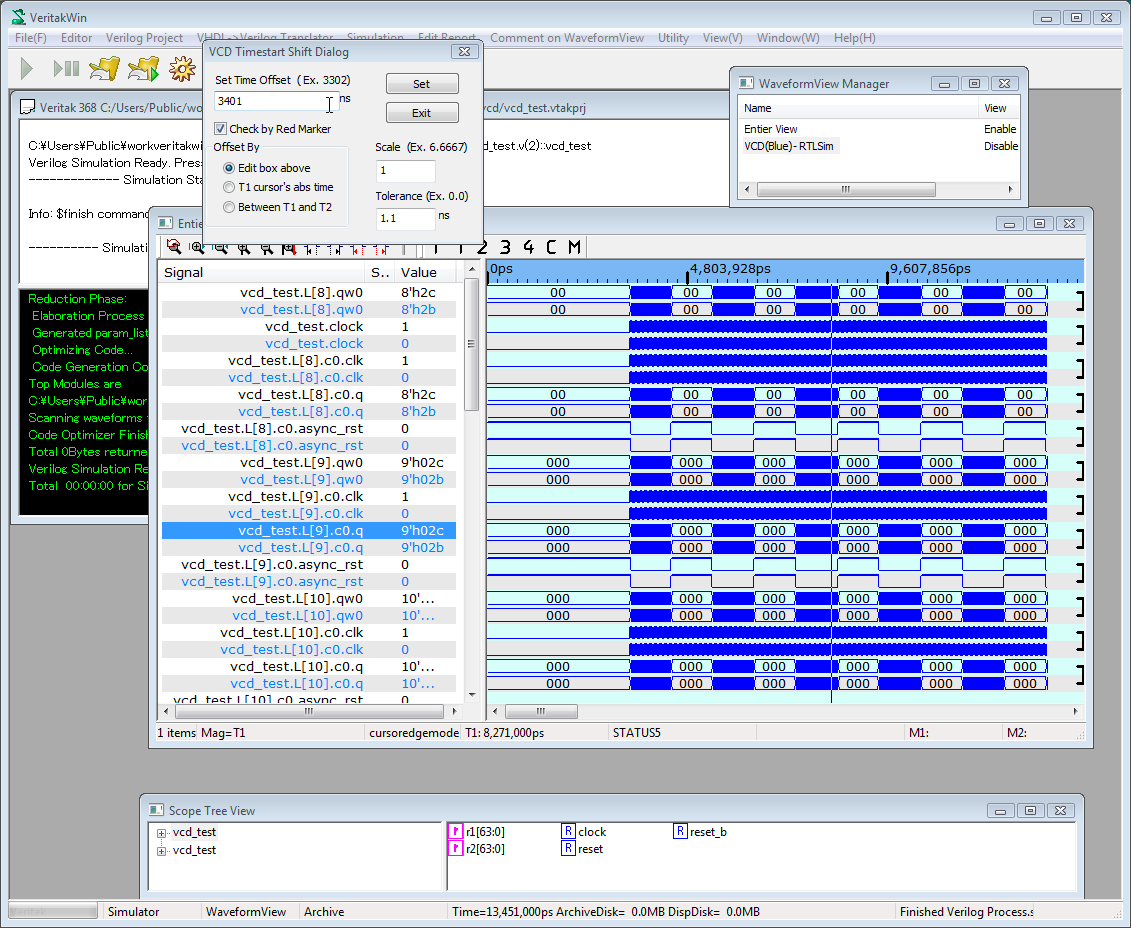

2.4.1.6 Waveform Comparison

You can compare two waveforms visually.

This function does not depend on the waveforms origin, VCD or Veritak.

Consecutive Two pair which have the same bit width are automatically compared.

Check by Red Marker enables different portions display by red as below.

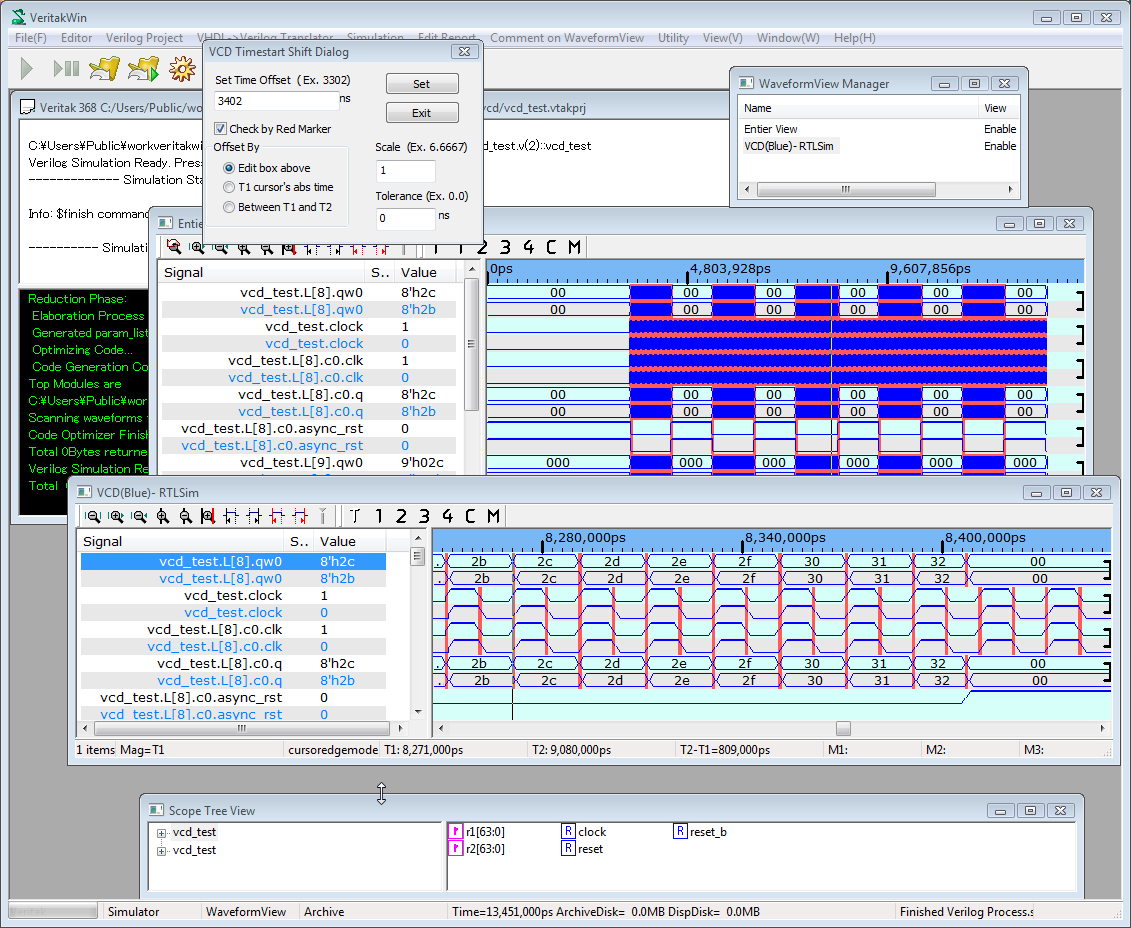

If No difference has detected ,then the display will be as follows.

Please note compared pair of waveforms are displayed as "]" at rightest position of the display. If "]" is not displayed, two waveforms are not compared because of incompatible

bit-width or due to some restrictions.

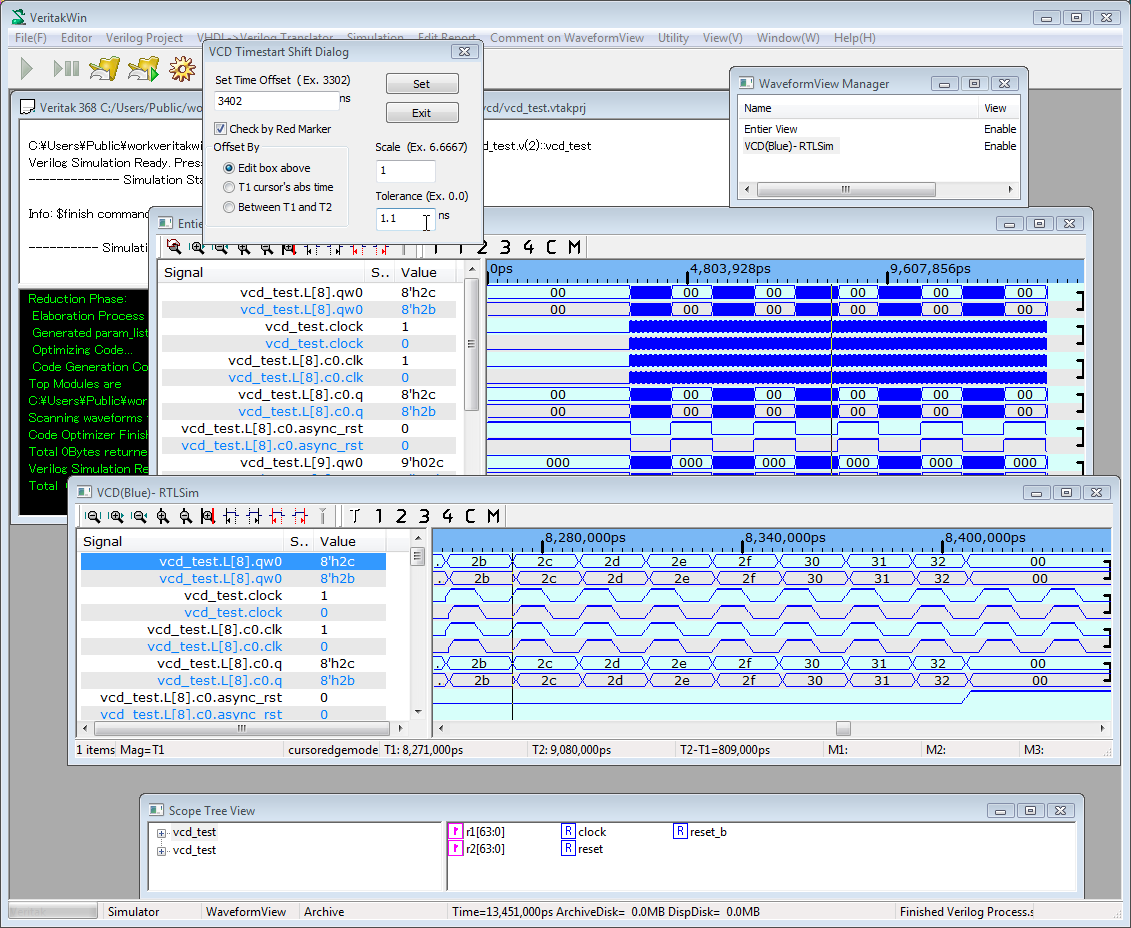

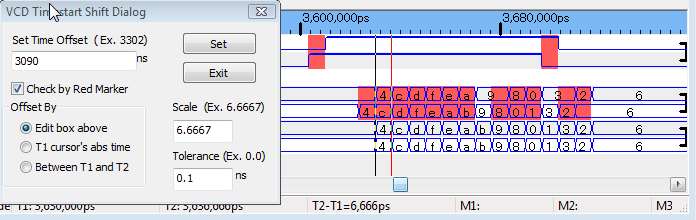

Tolerance

There may be some differences that must be neglected. Since algorithm displays

red-mark even if any glitch less than 1 dot-time in entire view, this

makes noisy in some situations. In such situation, you can define tolerance

as follows.

The display below shows 1ns shifted(3401->3402) vcd intentionally.

So, 1.1ns tolerance will filter those unwanted detections.

Tolerance examples

In the example below, VCD's floating scaling makes some jitter. To neglect

those glitch, we define 0.1ns tolerance.

Thus, successfully filtered those glitches.

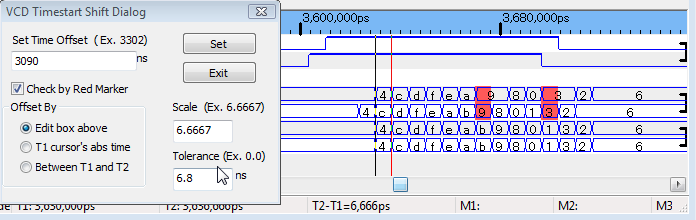

If we widen the tolerance than the cycle of externally sampled based VCD

,

can we ignore 1 clock shift?

Unfortunately, we can not do this. Following seems to be tricky but is

legal result in current algorithm.

TIPS