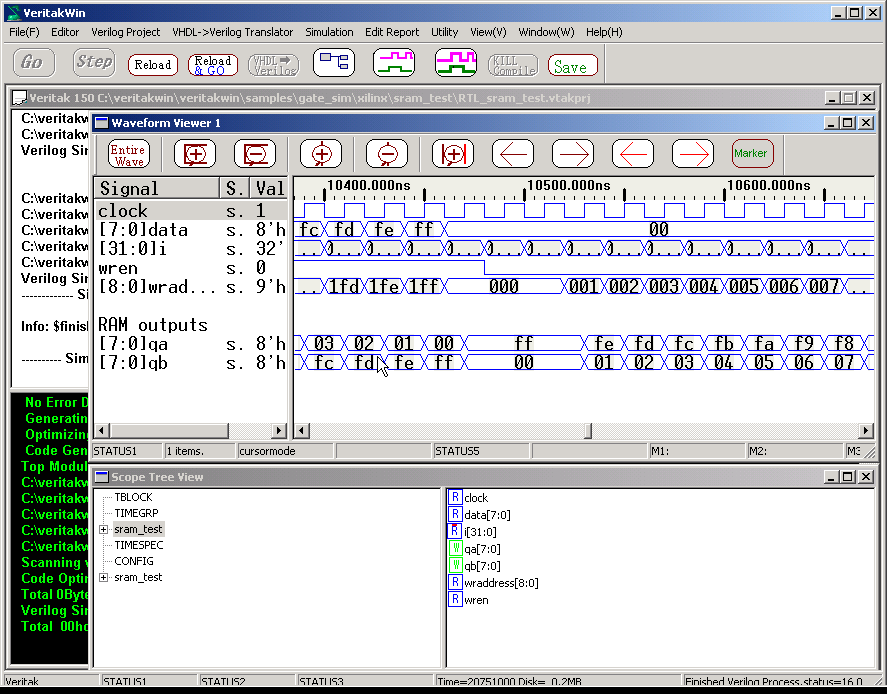

RTL Simulation

Here is RTL simulation using RAMB4_S8_S8.

Test bench is simple. Write data incrementally for entire 8-bit address space ,and read data incrementally for entire address space.

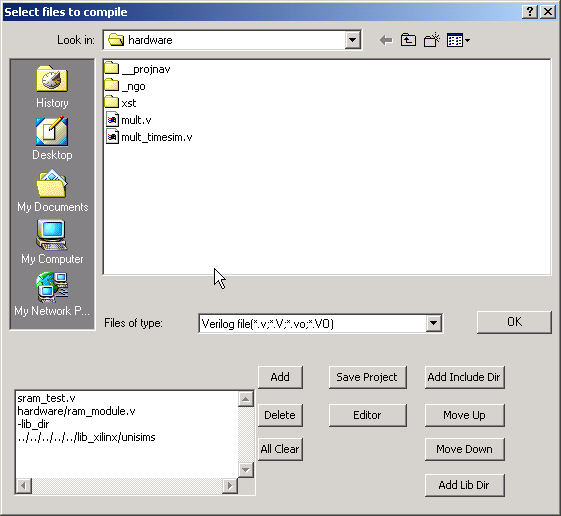

Here is hardware description, just wrapper for RAMB4_S8_S8 in Xilinx unisim library.

Here is Configuration of RTL project

You may use "RAMB4_S8_S8.v" instead of lib_dir "unisim" for faster compilation.

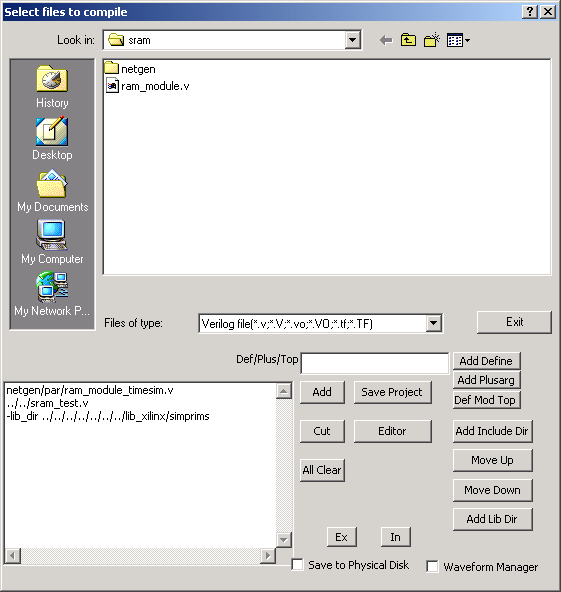

Gate simulation

Synthesize "ram_module" and generate ram_module_timesim.v and

ram_module_timesim.sdf..

Using these files, Gate Simulation configuration is as follows.

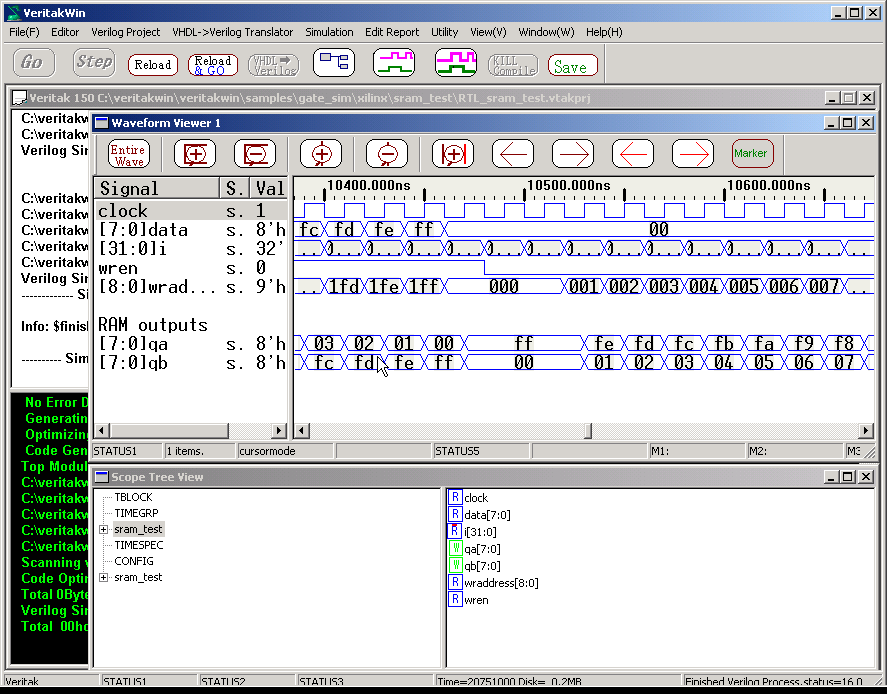

Figure below shows post-layout simulation results.

SDF timing error will be appeared about several nsec due to simulator's

transitional state on power on. Ignore errors on such duration