Basically trace mode2 is the same as trace mode except for generating tag

file which describes entire structure of design.

Let's look at the example.

Load Project "node_check_test.vtakprj"

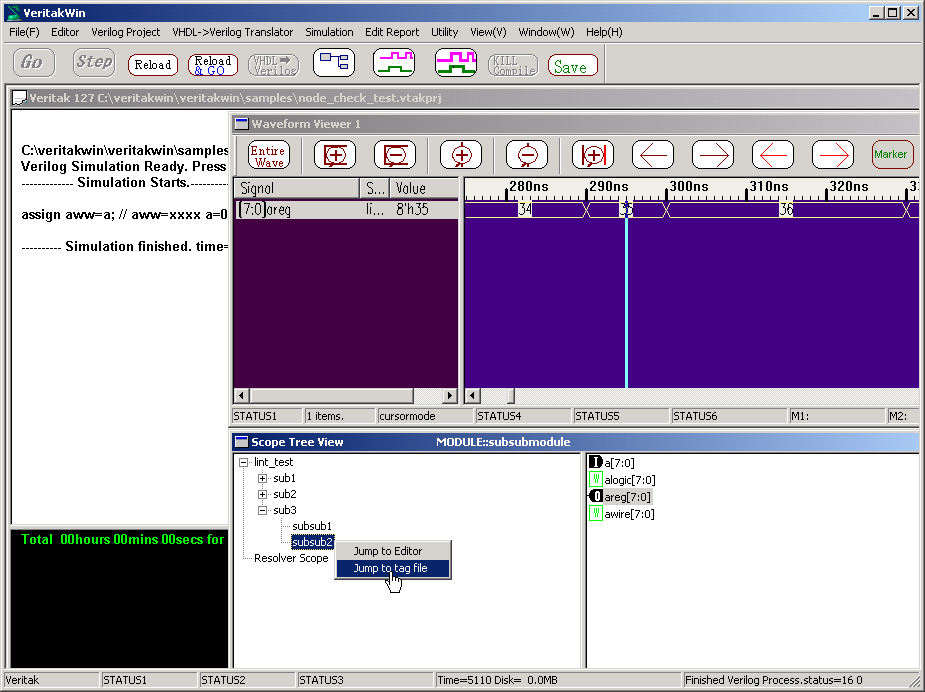

Jump to tag file as below.

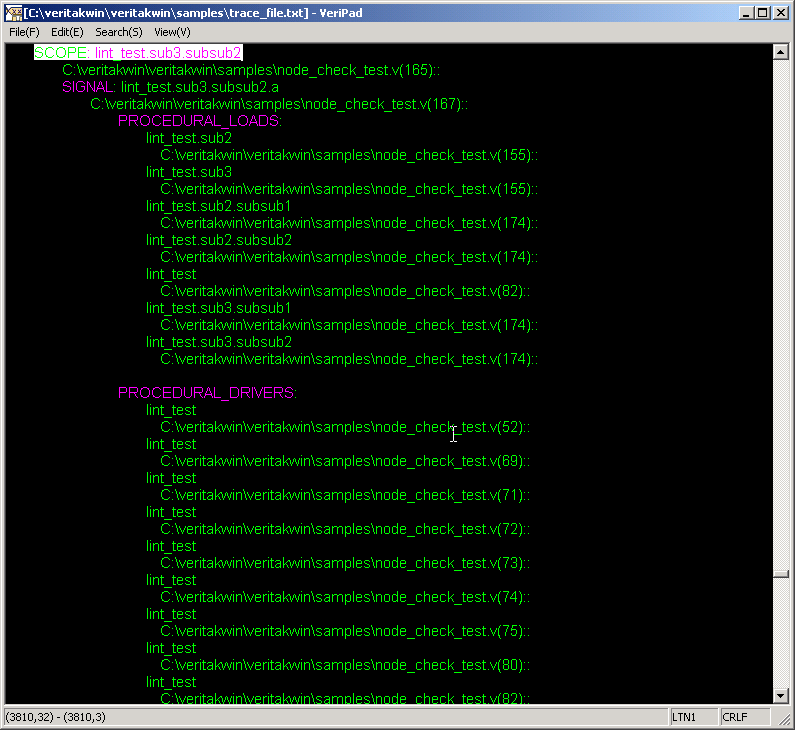

Here is tag file.

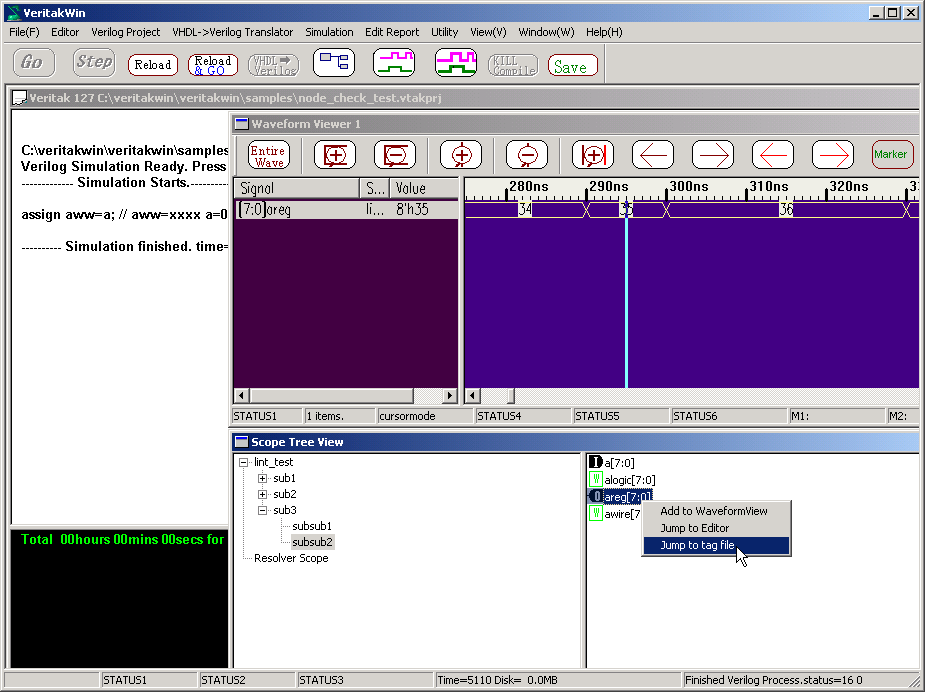

You can also jump to tag file from List view as well as from WaveformView.

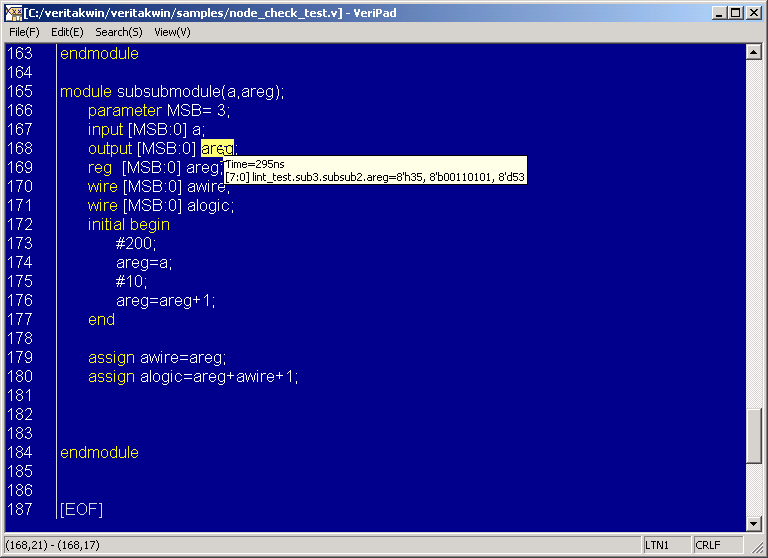

Double-Click "lint_test.sub3.subsub2.areg" at source driver in tag file.

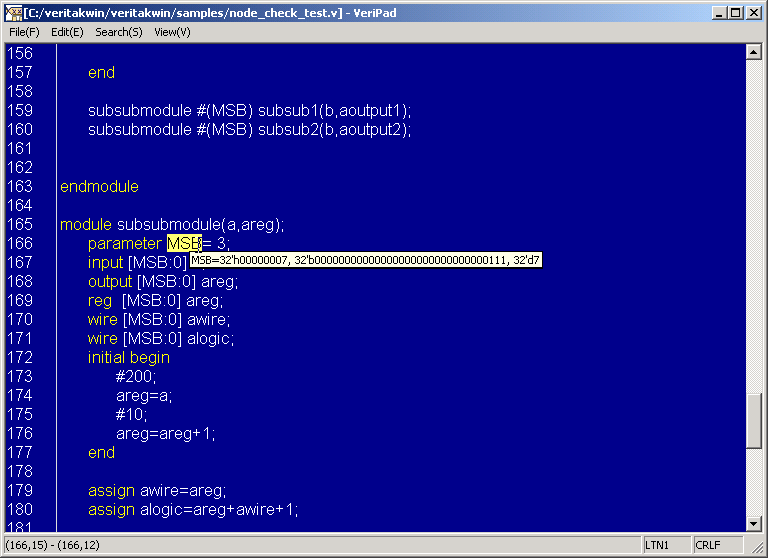

Then , jumped to Editor line 168.

Since tag file has not only file locational information but also Scope

information ,unique instance value can be tool-tipped as below,though susubmodule

has 6 instanced module. Time 295ns is derived from T1 cursor.

Instanced parameter also can be viewed.

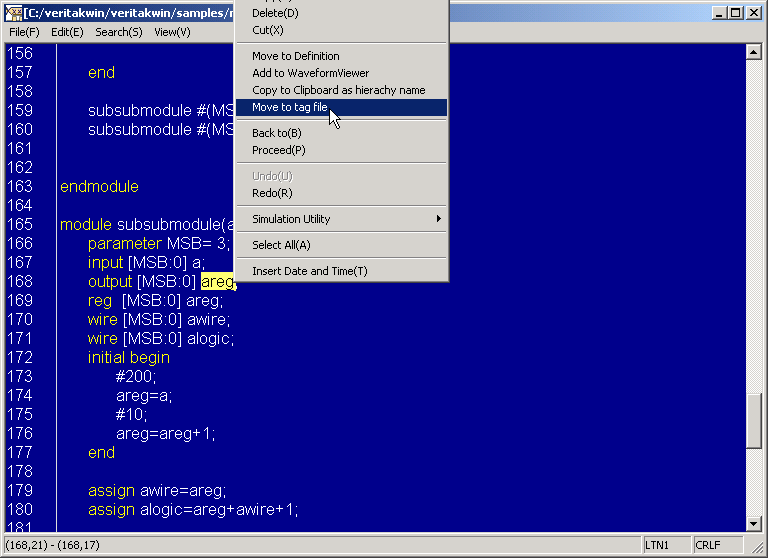

Veripad can jump to tag file.

Meaning of Keywords in tag file

As Keywords,SCOPE,SIGNAL,PROCEDURAL_LOADS,PROCEDURAL_DRIVERS,Aliases,SourceDriver,Drivers_FANOUTS,DECLARED,ASSIGNED

are defined.

| KEYWORD | Meaning | Example |

| SCOPE | Scope. followed by multiple "SIGNALF". | |

| SIGNAL | Signal. Not supported memory and long vector | |

| PROCEDURAL_LOADS | RHS in procedural statement. | initial a=b; if(b);//** a<=b; a<=b[i]; b's PROCEDURAL_LOADS are all statements. |

| PROCEDURAL_DRIVERS | LHS in procedural statement | a's PROCEDURAL_DRIVER are all statements except for ** in above. |

| Aliases | Alias. actually same signal but have different name. | In instanced module, sub dut(.clock(CLOCK)); clock and CLOCK is same signal |

| SourceDriver | Declaration of Driver | reg a;//here wire c;//here assign c=a ^ b; |

| Drivers_FANOUTS | RHS in net Structure | In above signal "a and b", assign c=a ^b; |

| DECLARED | Declaration | In above signal "c" wire c; |

| ASSIGNED | Assigned (Same as DECLARED in variable declaration.) | In above signal "c", assign c=a ^b; |

| ResolverInputs | Resolver's inputs |