2.4.23 Move Project without losing waveform view format

2.4.23.1 Xilinx

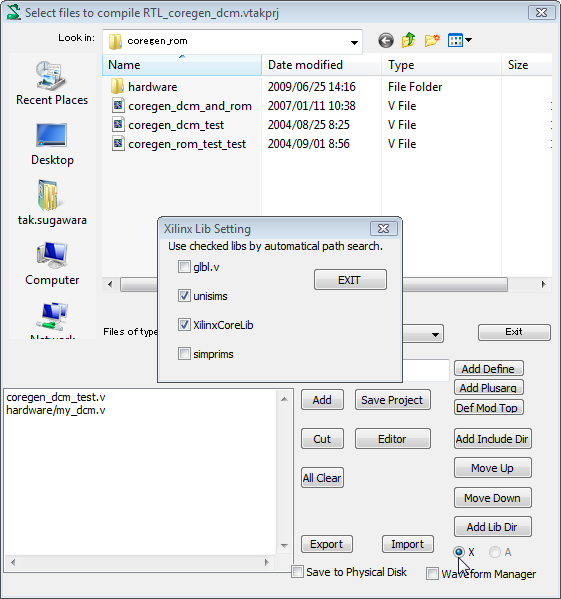

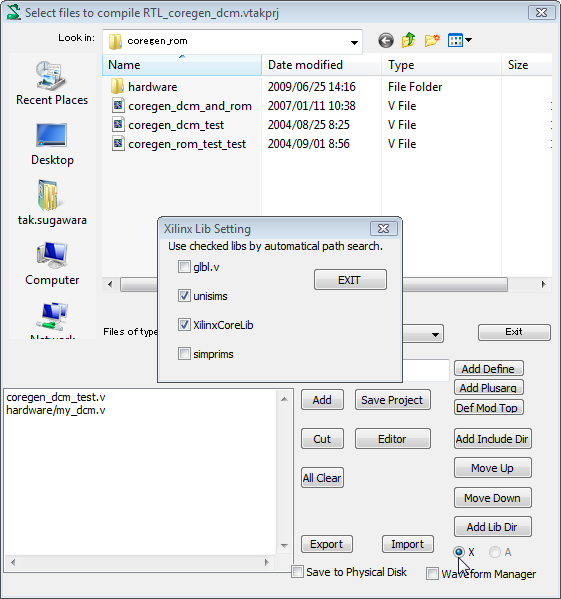

For Xilinx, you can select library as shown below instead of using Add Lib Dir.

This may be preferred because each libraries are searched automatically

using environmental variable.

It is to be noted to avoid double booking. For example, if you check unisims

, unisim in list box should be deleted by Cut.

Another note is waveforms should be displayed in this work, and press Save Project

That's all for necessary work for move. Please copy related folderers to

destination.

Tips:

- If you are using waveform manager, it is OK without waveformviews throughout

the operation..

2.4.23.2 Others

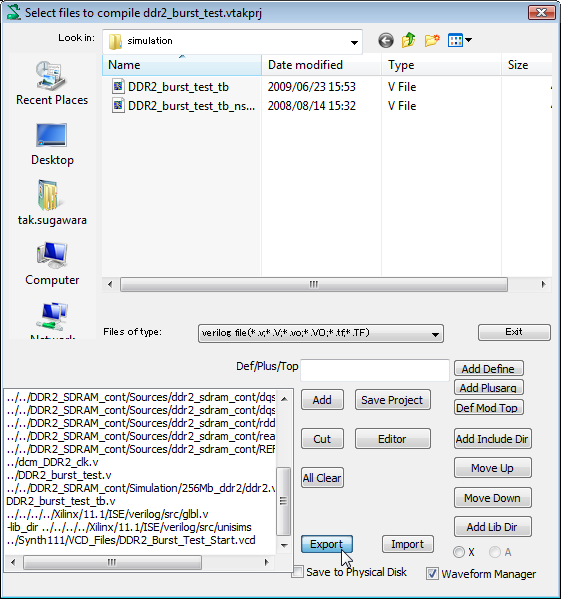

Use waveform manager before any operations in this section. This is necessary

for not losing waveform format information.

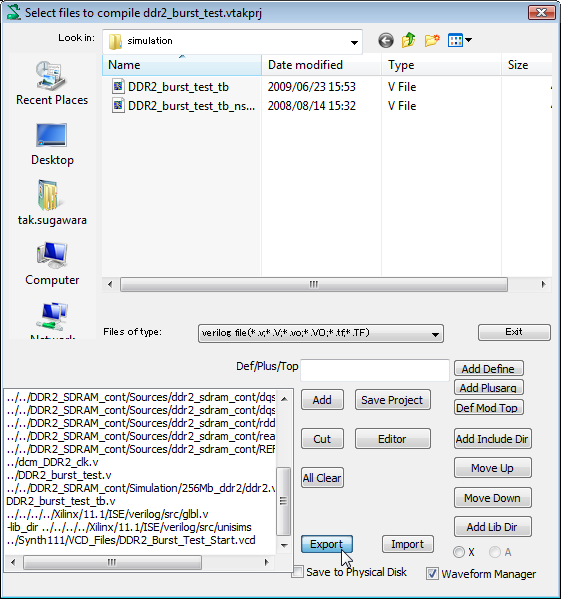

1) Operations in source folder

Export the project.

Then veritak_src_files.txt is should be in your project folder.

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/wrdata_fifo.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/addr_fifo.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/async_fifo_fall.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/async_fifo_rise.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/controller.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/dcm_module.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/ddr2_cont_iob.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/ddr2_sdram_cont.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/dm_io_pad.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/dq_io_pad.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/dqs_io_pad.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/dqsb_io_pad.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/rddata_afifo.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/read_write_io.v

../../DDR2_SDRAM_cont/Sources/ddr2_sdram_cont/REFREQSM.v

../dcm_DDR2_clk.v

../DDR2_burst_test.v

../../DDR2_SDRAM_cont/Simulation/256Mb_ddr2/ddr2.v

DDR2_burst_test_tb.v

../../../../Xilinx/11.1/ISE/verilog/src/glbl.v

-lib_dir

../../../../Xilinx/11.1/ISE/verilog/src/unisims

../Synth111/VCD_Files/DDR2_Burst_Test_Start.vcd

Please note all paths are described by relative path to the project folder. If your destination folder has the same relative paths,

there is nothing to do.

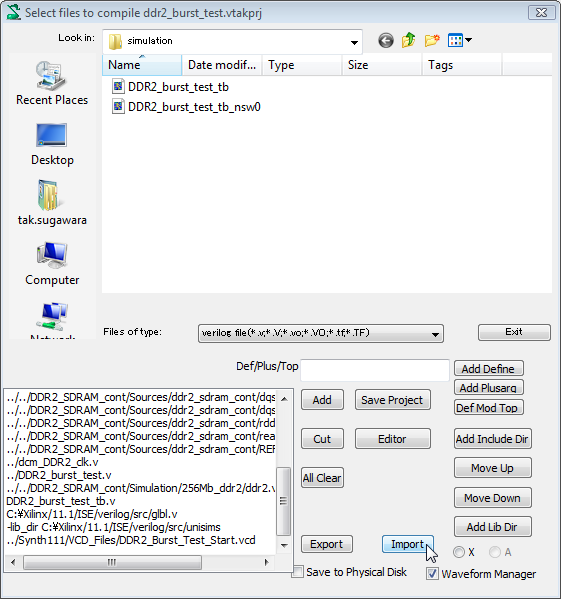

One of the likely problem is different library paths between source and

destination folders.

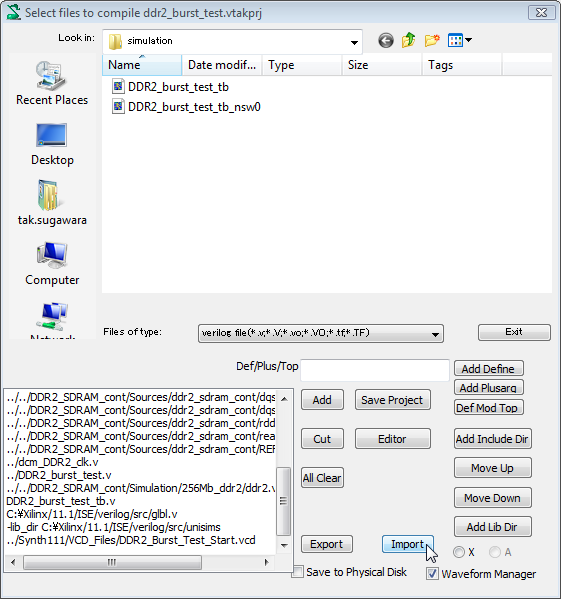

As an example, we re-write the path as below by text editor.

C:\Xilinx/11.1/ISE/verilog/src/glbl.v

-lib_dir

C:\Xilinx/11.1/ISE/verilog/src/unisims

We replaced the necessary paths to absolute path.

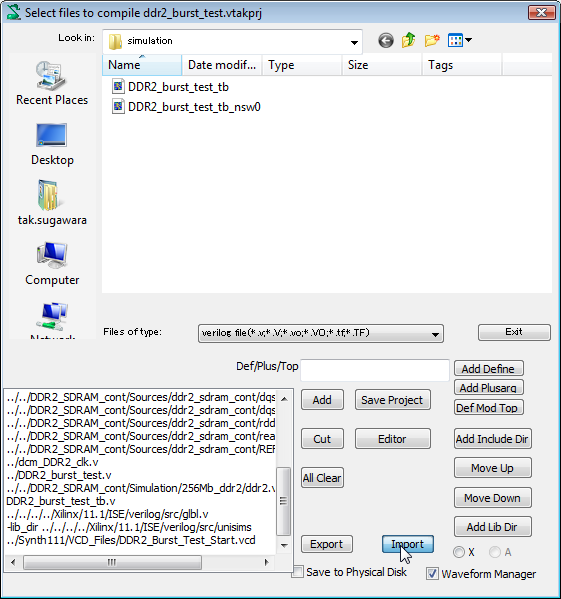

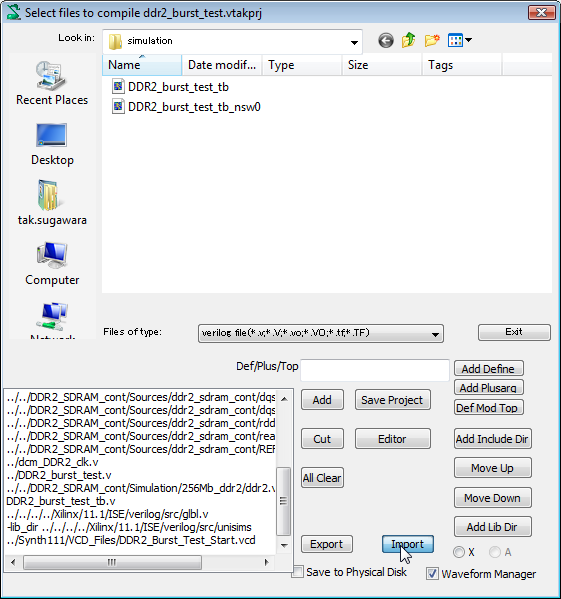

2) Operations in destination folder

Open Verilog Project. Press Import button

Then you'll find edited paths as below.

(Please neglect \. \ is Japanese \ )

Finally press Save Project button .