2.4.14 Define/Include/Library/$value$plusarg

2.4.14.1 Define

Let's look at example. Load project "samples/alu_test_w_ifdef.vtakprj

"

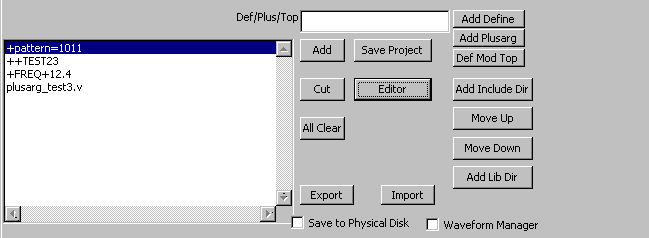

Following figure shows "Display_Epilog" is defined in the project.

it is equivalent to

`define Display_Epilog

in source description.

-Define here is valid for throughout the Project.As for -include_dir,please

place it before verilog file use it. ( See Project Setting for Define Propagation.)

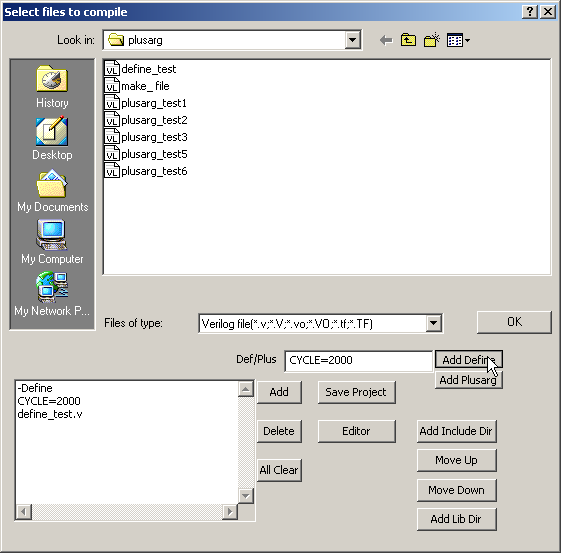

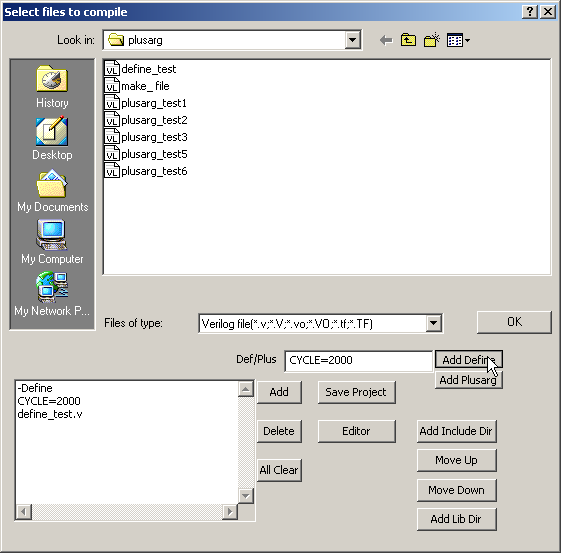

Here is another example. It is equivalent to

`define CYCLE 2000

in source description.

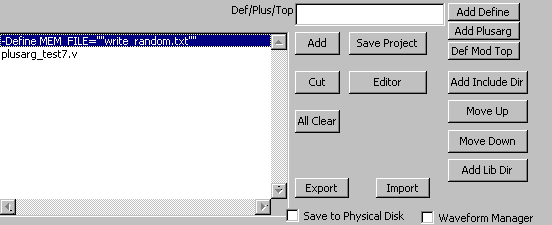

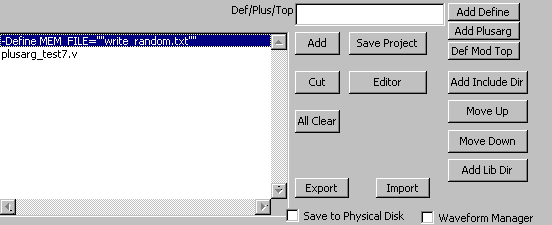

Note: about " "

When you use "double quotation ", please use "" instead of ". See an example below.

An example project is in "regression_test\plusarg".

2.4.14.2 Include

Please see "How to make project".

2.4.14.3 Library

Please see "Gate Simulation".( See also Project Setting for faster compilation)

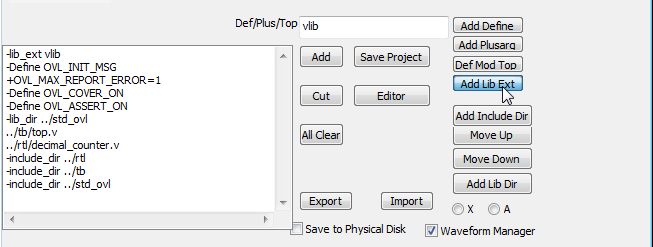

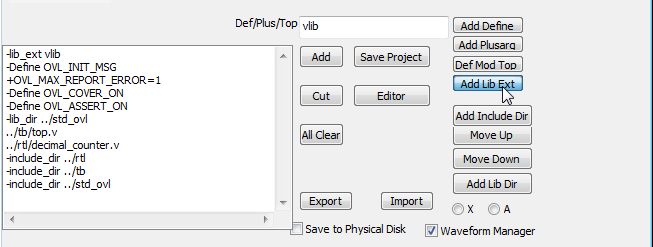

If library file's extension is not ".v", use Add Lib Ext per following example.

2.4.14.4 $value$plusarg ( Verilog 2001 )

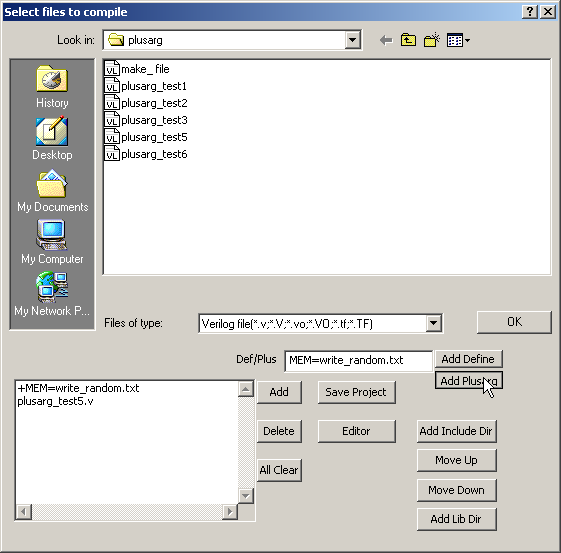

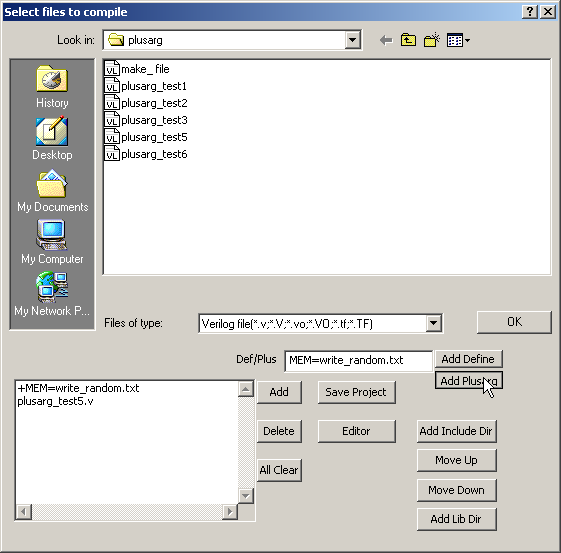

Define , for example, MEM=write_random.txt in the box below as $value$plusarg.

Then Press AddPlusarg.

See other examples in the folder of regression_test\plusarg. (sscanf.vtakprj is the most powerful example for usage of $value$plusarg).

This feature may be useful for regression tests by command line ,and

possibly result less re-compilation times for future release of compiled versions.

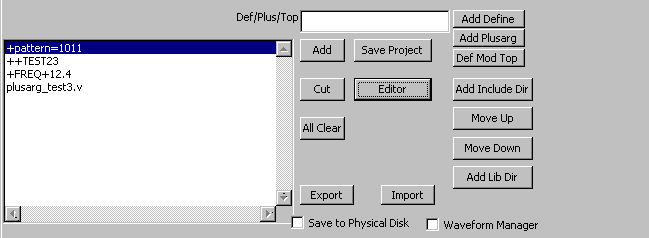

<Rapid Edit & Run>

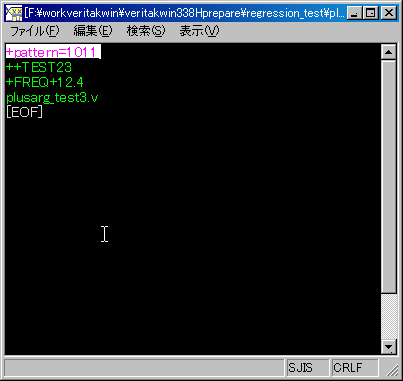

When you press Editor button with highlighting "-"or "+" line(Define/Plusargs Line)

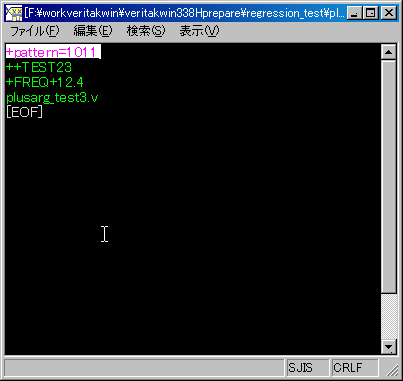

, Veripad opens it as "veritak_src_file.txt" as below.

This file can be exported/or imported by Export/Import button on Dialog above. It may be also useful when you edit source files

in the project by text, not GUI.

Close the dialog abovle, right-click on Veripad, select Simulation Utility->Save->Reload->Run

Then Veritak runs with changed parameter. Ctrl-T is short Cut Key.