RTL Project

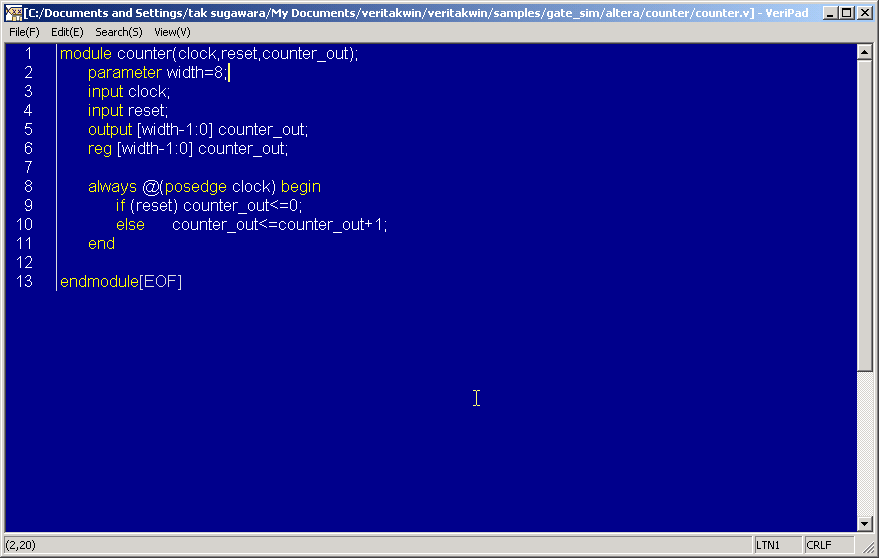

First, Let's look at the RTL project "RTL_counter.vtakprj" (/samples/altera/counter/)

This is simple 8-bit incremental counter.

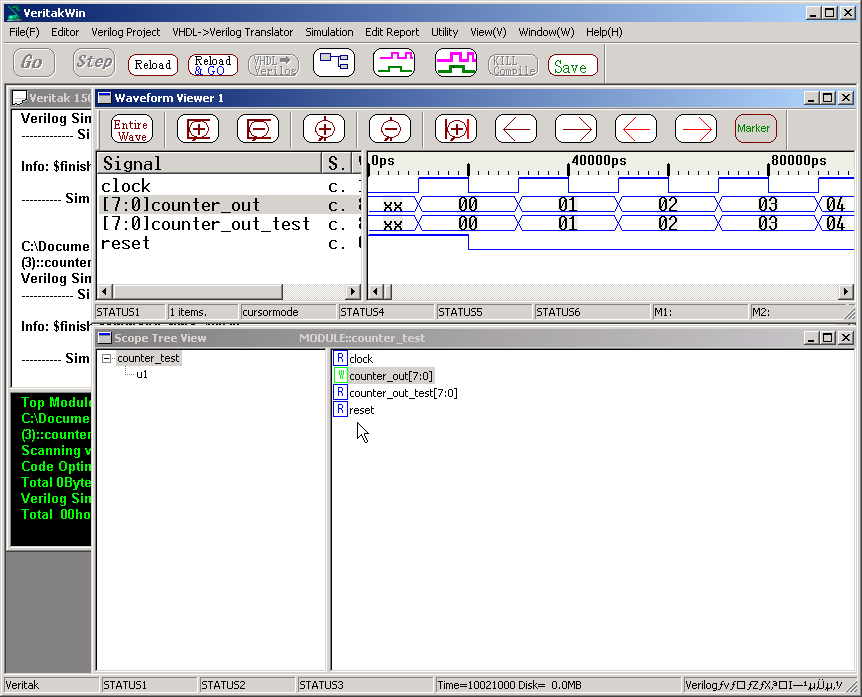

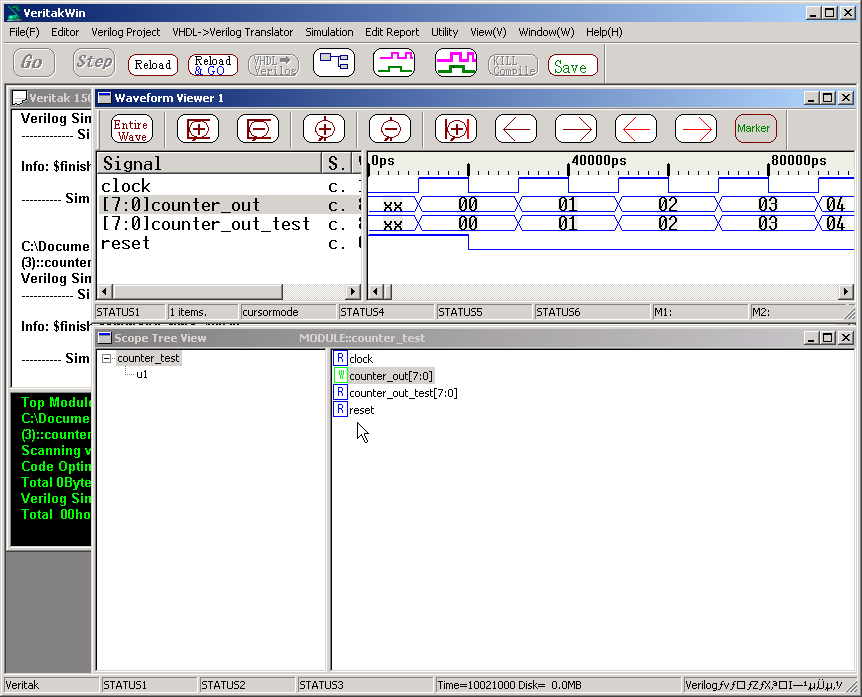

RTL Project

First, Let's look at the RTL project "RTL_counter.vtakprj" (/samples/altera/counter/)

This is simple 8-bit incremental counter.

RTL source is simple.

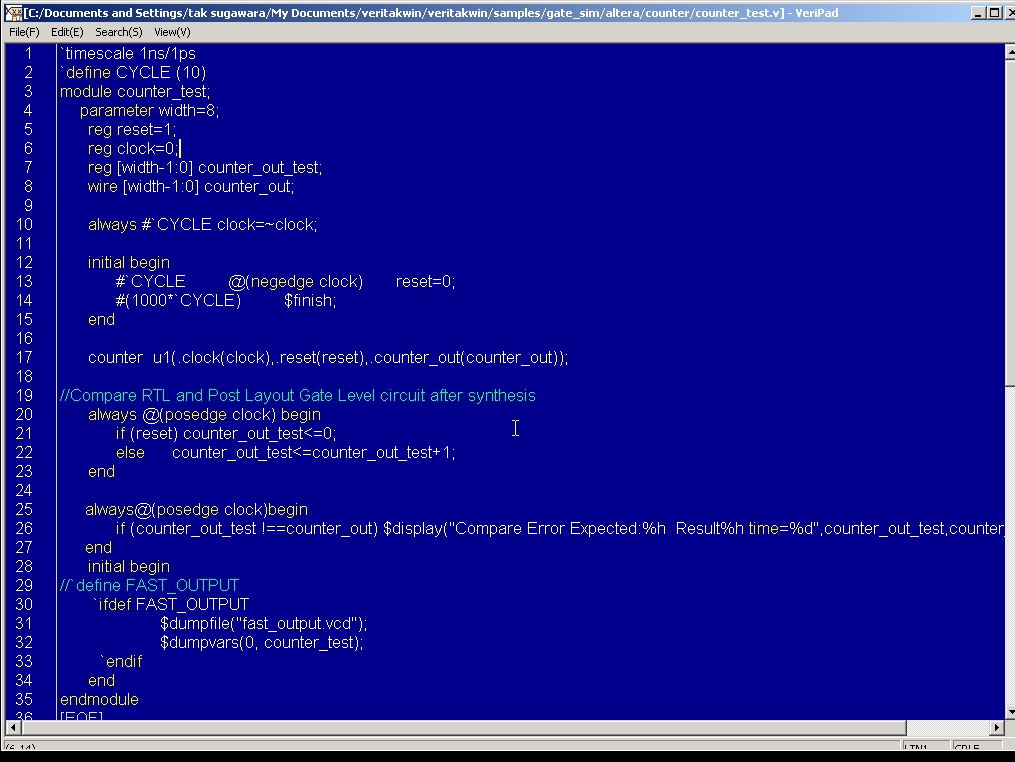

Test bench is

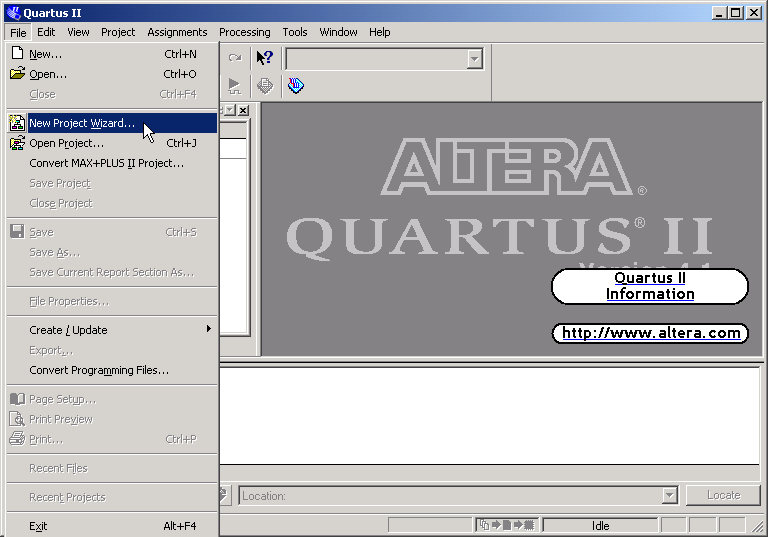

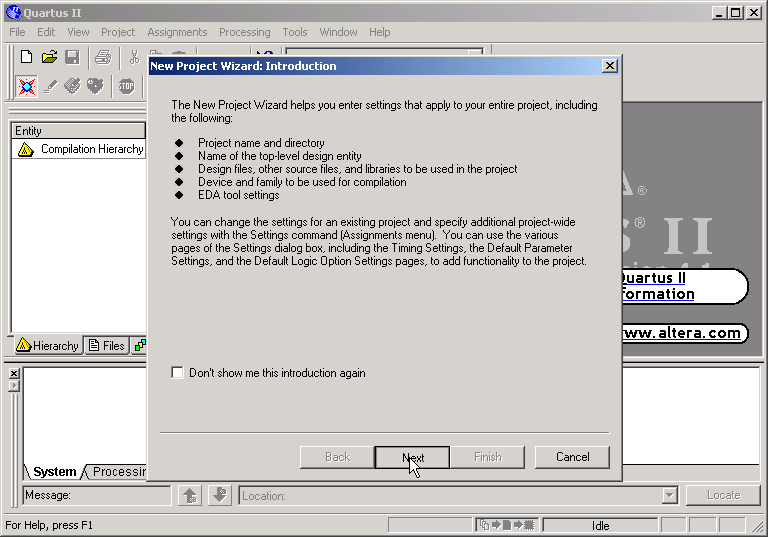

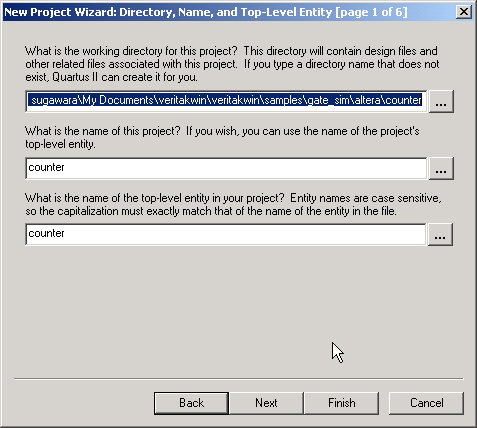

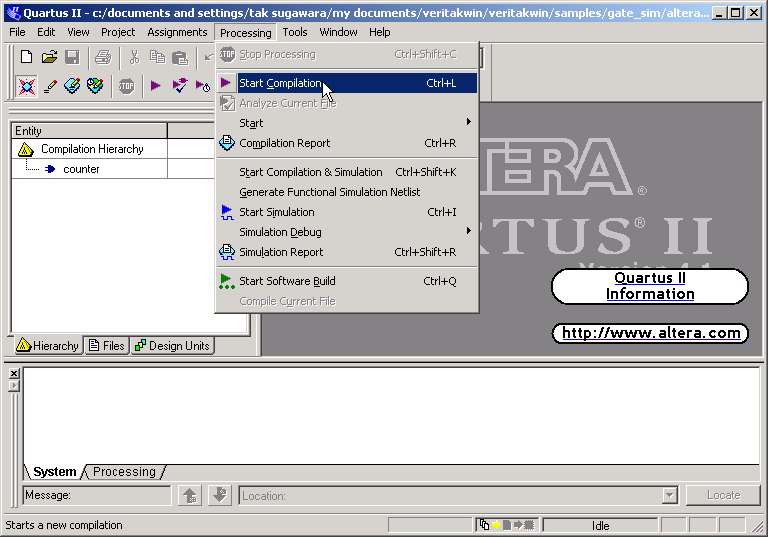

Quartus Setting Make New Project with Quartus

Next,

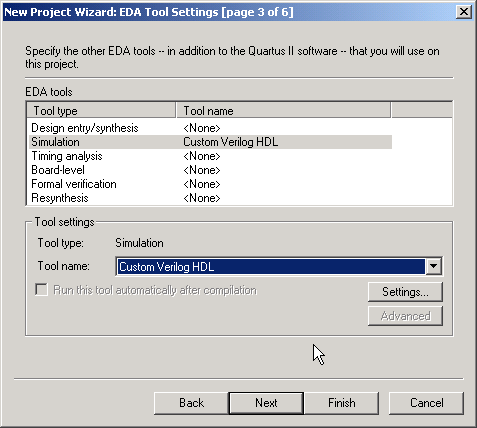

Since Simulation tool here is Veritak, set as below

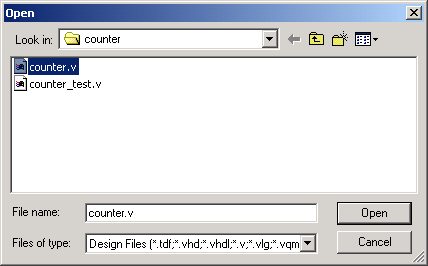

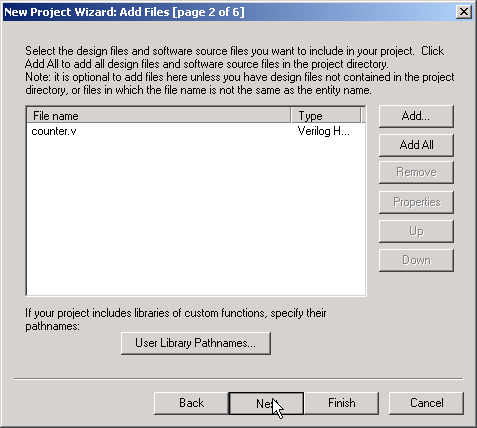

Next, and select "counter.v" for synthesis

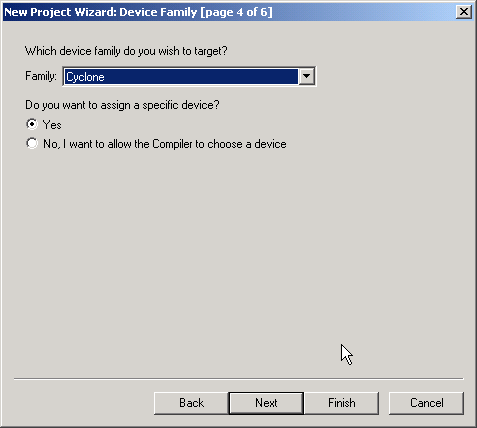

Device is as you like..(Cyclone,Stratix, Stratix2,Cyclone2)

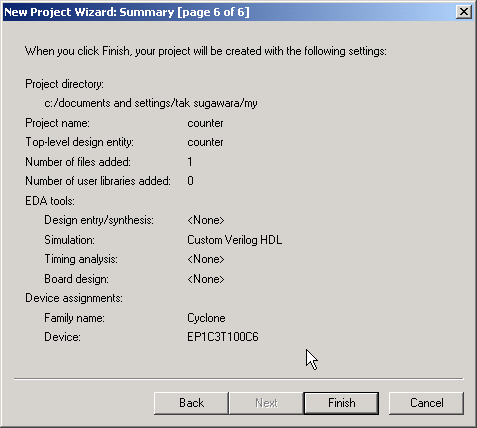

Finally you will get following summary.

Finished making project with Quartus. Let's start compilation.

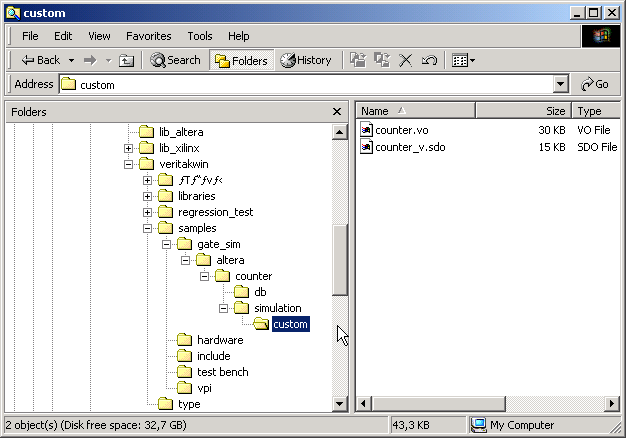

After success of compilation, you should see files below.

*.vo is synthesized gate description generated with verilog for simulation.

*.sdo is delay file, will be read by " $sdf_annotate(... )" in *.vo

file in gate simulation runtime.

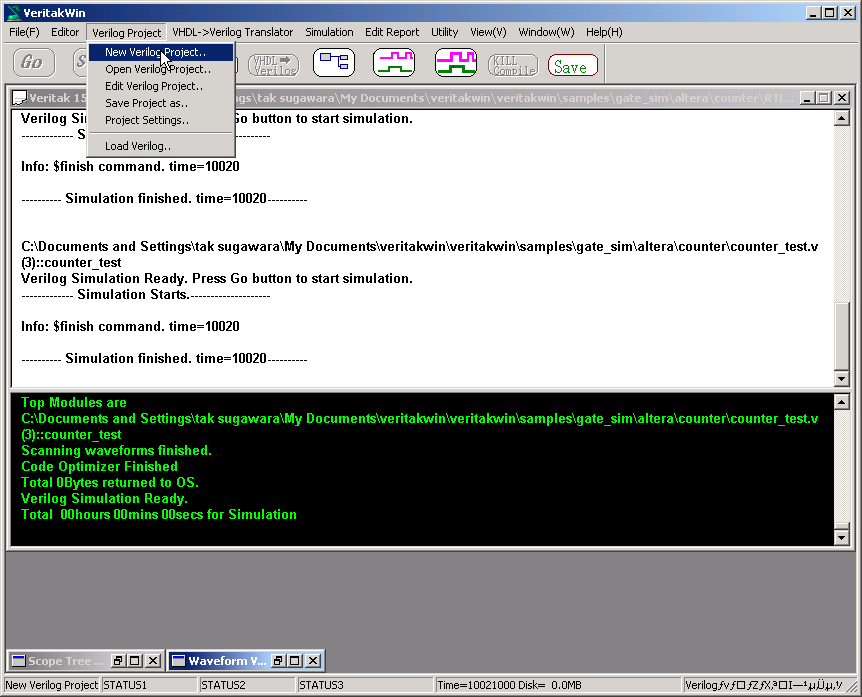

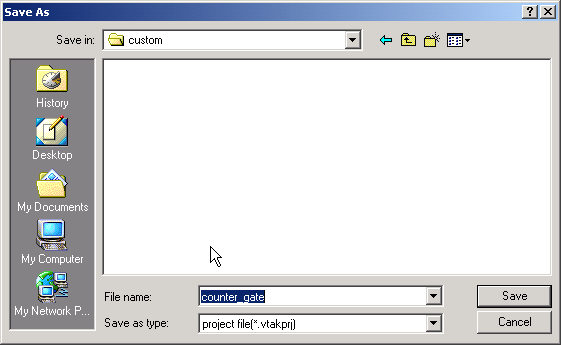

Now synthesis is complete, let's make Veritak Project for gate simulation.

Gate simulation Project in Veritak must be in the same folder where *.vo and *.sdf file exist.

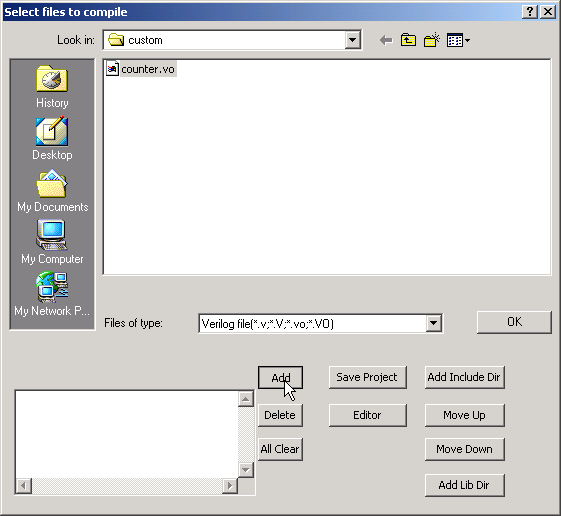

Add synthesized file.

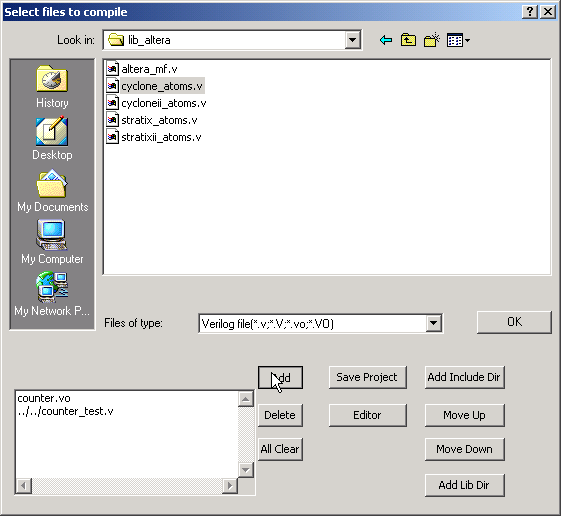

Add test-bench file

Add primitive library file for selected device.

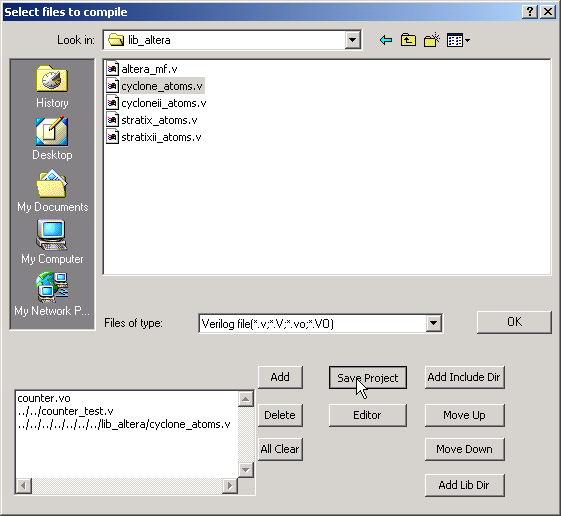

Final configuration in project is as follows. Do not forget to save the project.

Gate Simulation

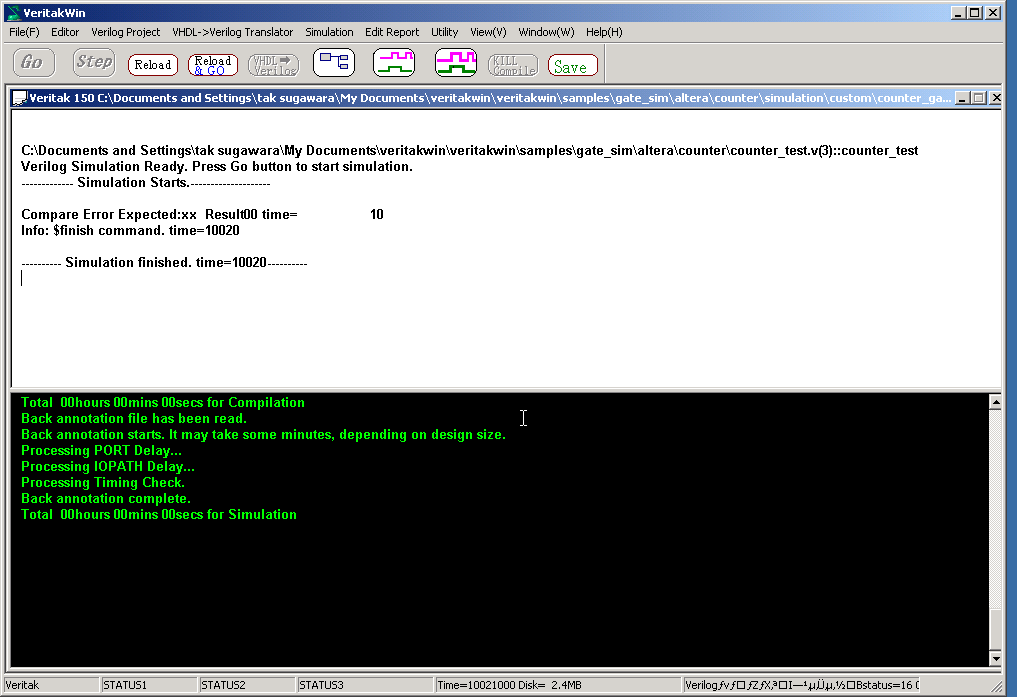

Load Verilog Project "couter_gateprj", and Go.

You see compare error in console. This is caused by difference of power on initial value between RTL and Gate-level device in Altera.

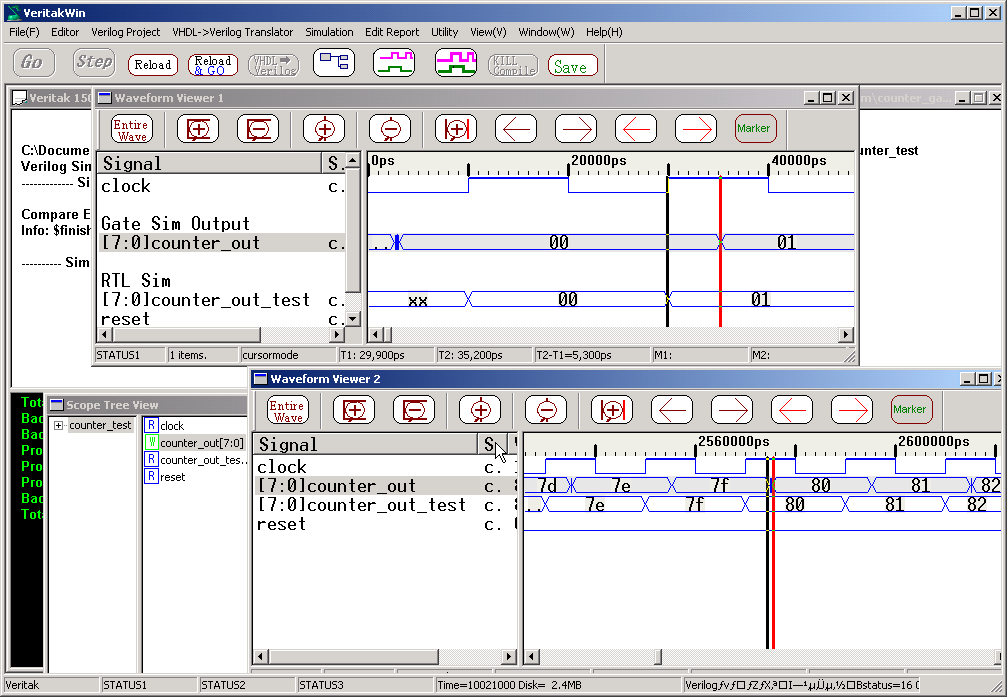

You can see RTL and gate-level waveform in figure.

At posedge of clock, counter output is incremented with delay 0 on RTL,

with some delay in gate-level simulation.

You can see Black-Reg cursor in fig. is 5300ps, that means clock-counter_out

path is 5300ps at Time 29.9ns. Please note that delay here is dynamic delay,

not maximum static delay. Maximum Frequency is reported in synthesis tool,

that is real maximum delay. It is to be noted dynamic delay is always less

than or equal to maximum static delay.

.

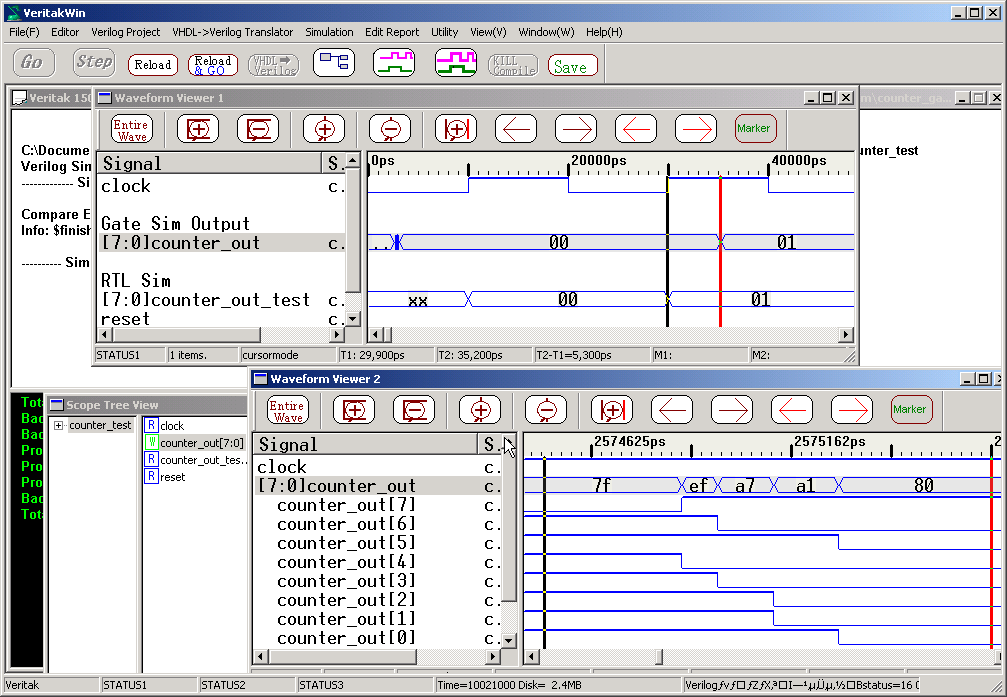

Following waveform shows all the pin delay is not the same.

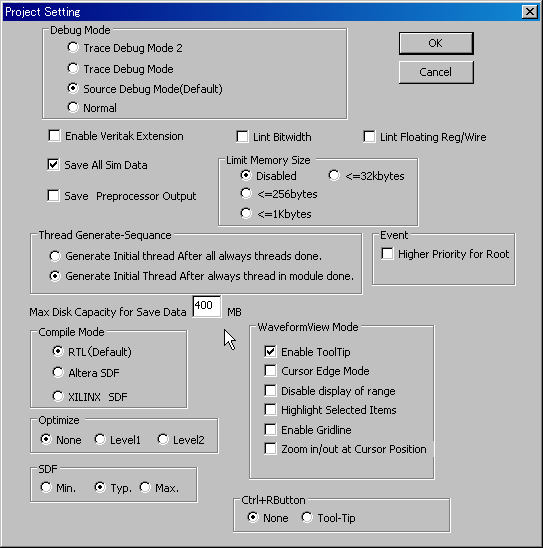

You can select Min/Typ/Max for SDF delay in Project Setting Dialog.. However nothing will be changed as for Altera/Xilinx because the same values are generated in SDF of Altera/Xilinx.