7 Examples of C compilation

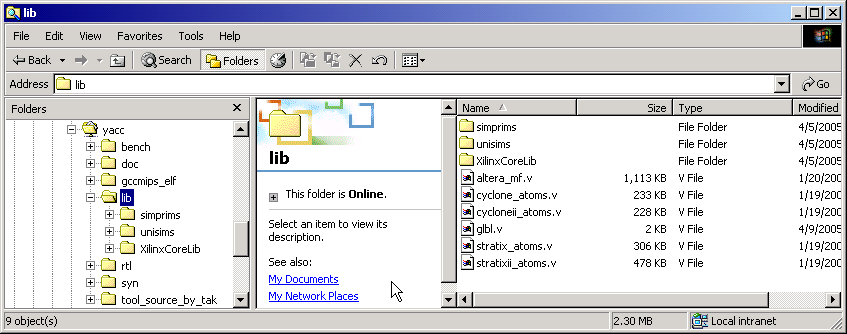

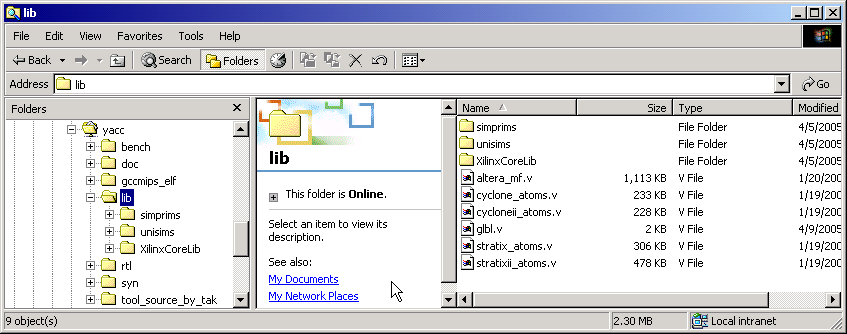

FPGA Vendor's library is not attached since they are property of vendors.

Set them under \lib folder as below to run RTL/Delay simulation in Veritak.(XilinxCorelib

is not attached in free Web Edition. BaseX or higher edition will be necessary.)

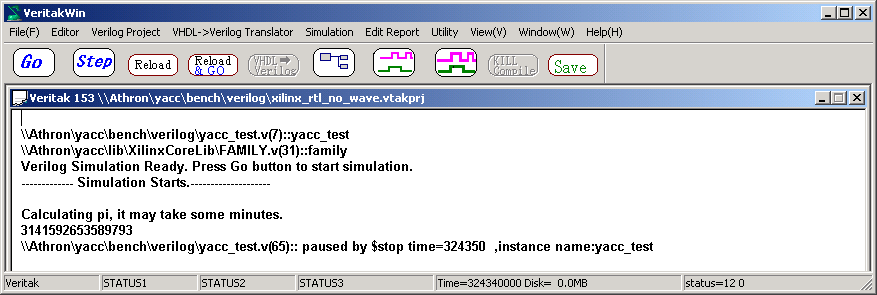

7.1 RTL

In RTL simulation using UART is too slow for debugging the cpu. Therefore output is changed

to console instead of UART PORT. Please note RTL

simulation takes very long time in running actual 10msec .

Veritak RTL projects are

- xilinx

- altera

- generic (no fpga library used)

| Folder |

C Program |

Description |

Batch File |

Veritak Project(\bench\verilog) |

| \bench\c_src\count |

count_tak.c |

By Steve Rhords |

compile.bat |

altera_rtl/xilinx_rtl/generic_ram_rtl |

| \bench\c_src\pi |

pi2.c |

pi 10digits |

compile.bat |

altera_rtl_no_wave/xilinx_rtl_no_wave/generic_ram_no_wave |

| \bench\c_src\dhrystone |

dhry21_tak.c |

Dhrystone |

compile.bat |

altera_rtl_no_wave/xilinx_rtl_no_wave/generic_ram_no_wave |

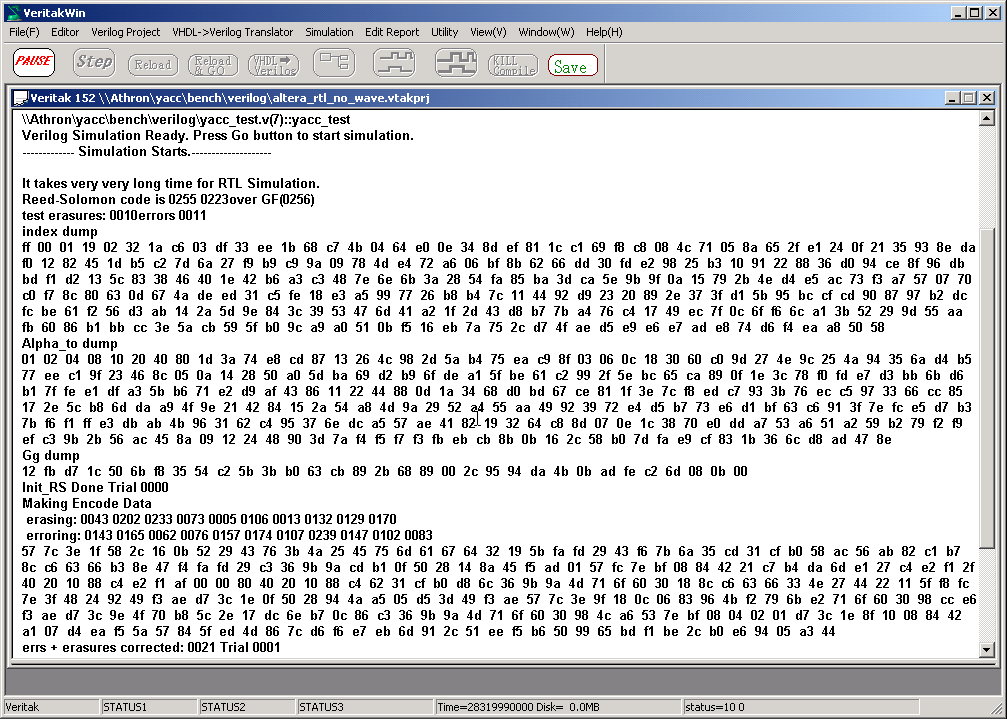

| \bench\c_src\reed solomon |

rs_tak.c |

By Phil Karn |

compile.bat |

altera_rtl_no_wave/xilinx_rtl_no_wave/generic_ram_no_wave |

| \bench\c_src\calculator |

uart_echo_test.c |

Interactive Calculator. Interrupt debug use |

compile.bat |

altera_calculator_test_using_uart_echo/xilinx_calculator_test_using_uart_echo

/generic_ram_calculator_test_using_uart_echo |

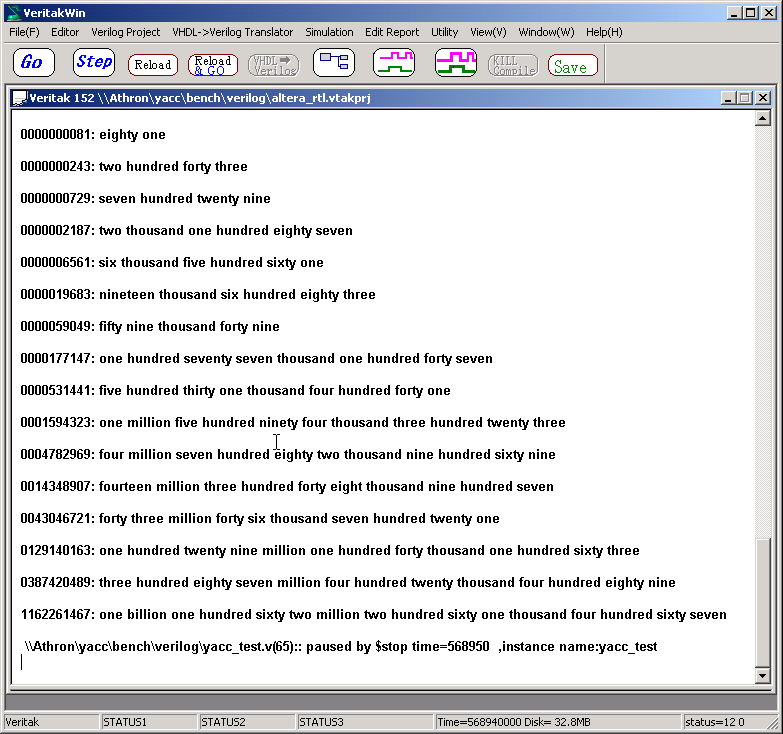

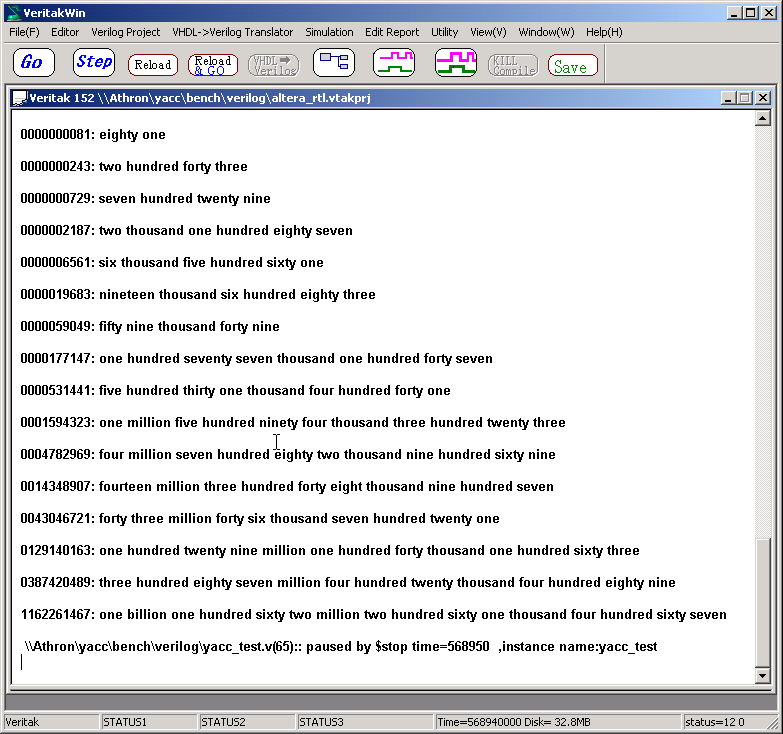

(1) count

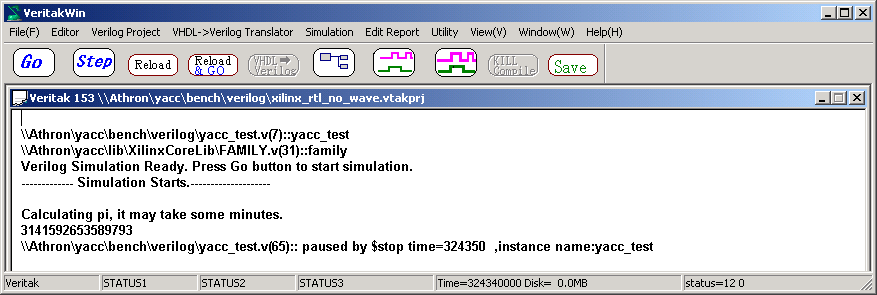

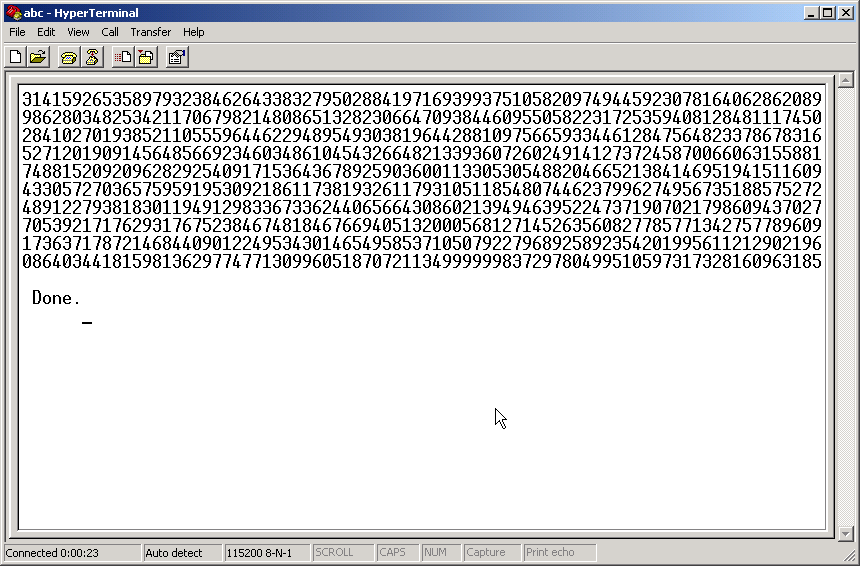

(2)Pi

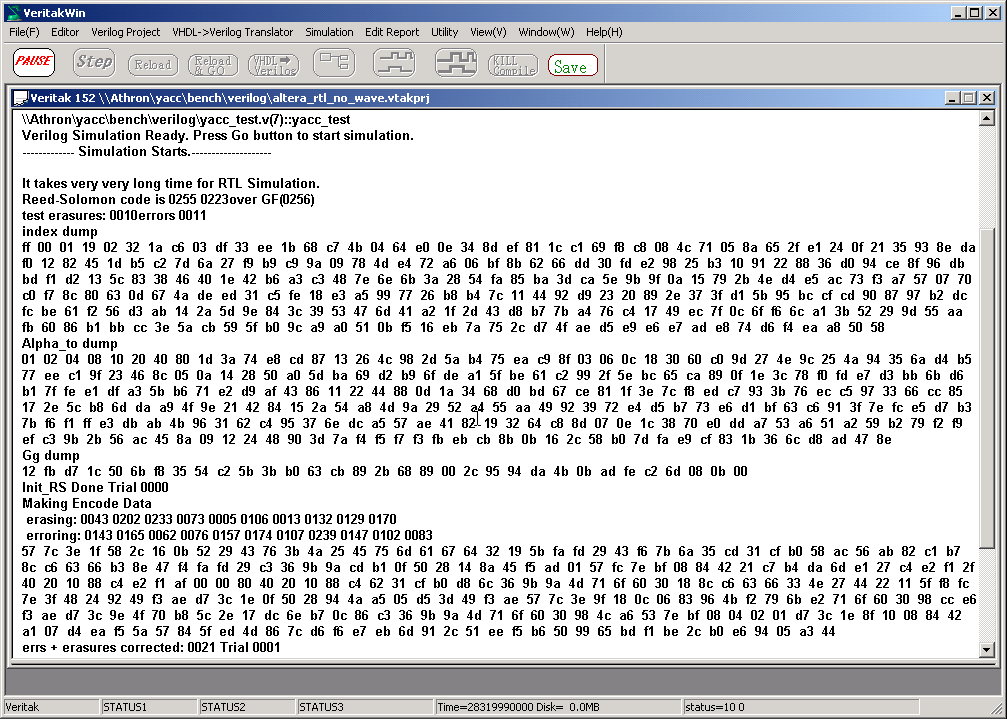

(3)Reed Solomon

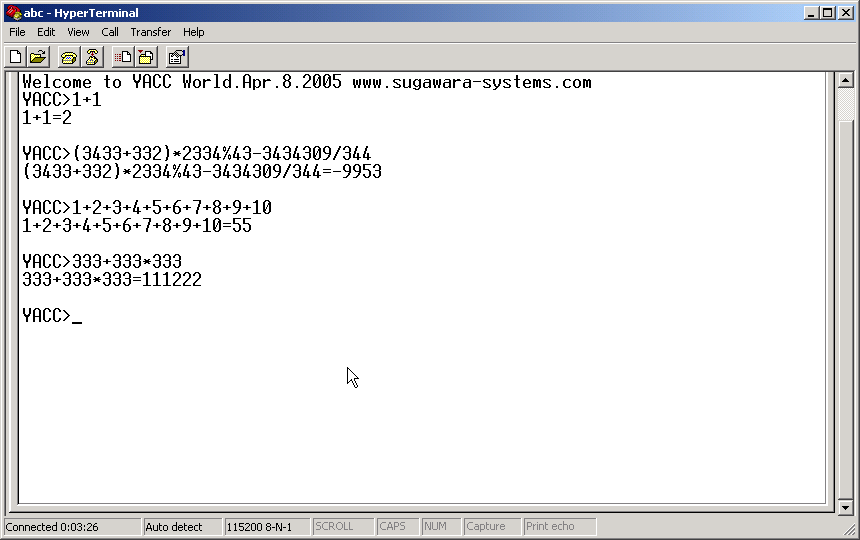

(4) Calculator

This is console output only, not interactive. Using echo-back technique,

UART interrupt test was done.

RTL Simulation Procedure

- Compile C program using compile.bat

- conver_mips.exe will generate memory initialization file for both altera/xilinx/generic,which

will be sent to\rtl\xilinx , \rtl\altera and \rtl/generic.

- Load Veritak Project=>Go

7.2 Gate Simulation

Using "count" above,Post-Layout Gate Simulation was performed.

| Folder |

Veritak Project File |

Frequency |

| \syn\altra_stratix2\simulation\custom |

Gate_altera |

165MHz |

| \syn\altera\simulation\custom |

Gate_altera |

100MHz |

| \syn\xilinx |

Gate_xilinx |

25MHz |

7.3 FPGA

| Folder |

C Program |

Batch File |

Description |

| \syn\c_src\count |

count_tak.c |

compile.bat |

By Steve Rhords |

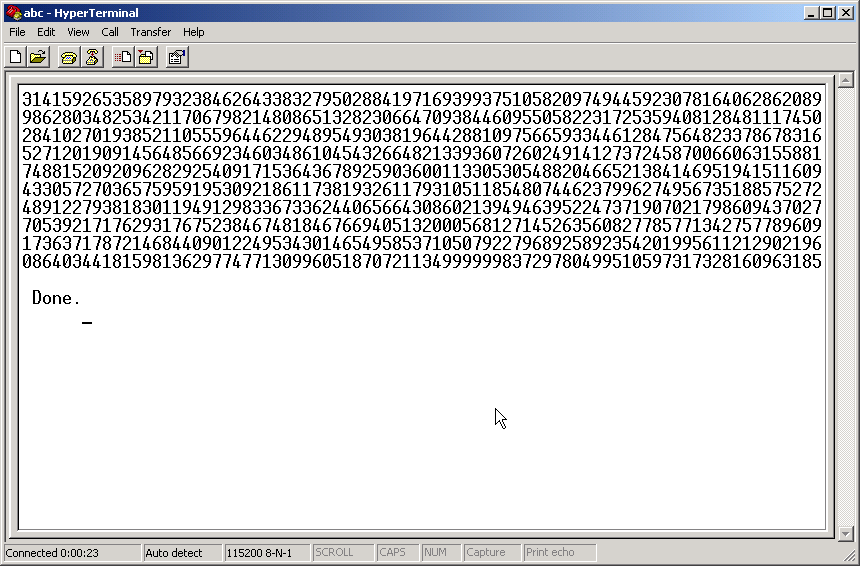

| \syn\c_src\pi |

pi2.c |

compile.bat |

pi 800 digits calculation |

| \syn\c_src\reed solomon |

rs_tak.c |

compile.bat |

By Phil Karn |

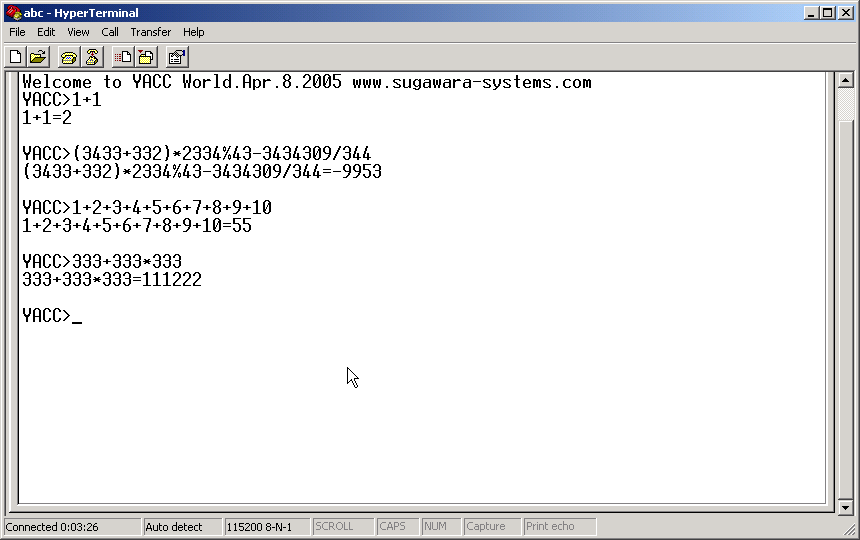

| \syn\yacc\bench\c_src\calculator |

uart_echo_test.c |

compile.bat |

Interactive Calculater |

<Synthesis Procedure>

- Run Batch File

- Synthesize top of hardware Regenerate RAM using core-generator, then Synthesize

top of hardware

FPGA Confirmation

| FPGA |

FPGA BOARD |

Device |

Clock |

CPU

CLOCK |

UART Baud Rate |

Synthesized by |

| Altera |

Future Electronics Cyclone/Nios II Development Board |

EP1C12Q240C6 |

50MHz |

50MHz |

115.2KBPS |

Quartus4.2 |

| Xilinx |

Xilin Spartan3 Starter Kit |

XC3S200-4FT256C |

50MHz |

25MHz |

57.6KBPS |

ISE7.1 |

Future Electronics Cyclone/Nios II Development Board

Spartan3 Starter Kit

(1) count

Same as RTL simulation except for endless loop.

(2) pi

3.1415...follows by 800 digits.It was the same

result as PC.

(3)Interactive Calculator

Use PC terminal software.You can calcuate like C program.

(4) Reed Solomon

Very Complex program (255,223) performs 120 cycles of 21bytes correction(including

erasures). No miss-correction is detected.