2.1 hello_uart

Evaluation of OPENRISC CPU

1. Environment

Let's make environment under cygwin.

Here is a makefile on hello_uart. You need to change the

following line for your environment on each makefile.

cp *.ihex f:/orp_soc/rtl/verilog/mem_if

ifndef CROSS_COMPILE

CROSS_COMPILE = or32-uclinux-

CC = $(CROSS_COMPILE)gcc

LD = $(CROSS_COMPILE)ld

NM = $(CROSS_COMPILE)nm

OBJCOPY = $(CROSS_COMPILE)objcopy

OBJDUMP = $(CROSS_COMPILE)objdump

endif

export CROSS_COMPILE

.SUFFIXES: .or32

all: hello.or32

reset.o: reset_with_cache.S Makefile board.h

$(CC) -g -c -o $@ $< $(CFLAGS) -Wa,-alnds=$*.log

hello.o: hello.c Makefile board.h

$(CC) -g -c -o $@ $< $(CFLAGS) -Wa,-alnds=$*.log

hello.or32: reset_with_cache.o hello.o Makefile

$(LD) -Tram.ld -o $@ reset_with_cache.o hello.o $(LIBS)

$(OBJCOPY) -O srec $@ $*.srec

$(OBJCOPY) -O ihex $@ $*.ihex

$(OBJDUMP) -S $@ > $*.S

cp *.ihex f:/orp_soc/rtl/verilog/mem_if

System.map: hello.or32

@$(NM) $< | \

grep -v '\(compiled\)\|\(\.o$$\)\|\( [aUw] \)\|\(\.\.ng$$\)\|\(LASH[RL]DI\)' | \

sort > System.map

#########################################################################

clean:

find . -type f \

\( -name 'core' -o -name '*.bak' -o -name '*~' \

-o -name '*.o' -o -name '*.a' -o -name '*.tmp' \

-o -name '*.or32' -o -name '*.bin' -o -name '*.srec' -o -name '*.ihex' \

-o -name '*.mem' -o -name '*.img' -o -name '*.out' \

-o -name '*.aux' -o -name '*.log' \) -print \

| xargs rm -f

rm -f System.map

rm -f onchip_ram_bank?.mif

rm -f onchip_ram_bank?.v

rm -f hello.S

distclean: clean

find . -type f \

\( -name .depend -o -name '*.srec' -o -name '*.bin' \

-o -name '*.pdf' \) \

-print | xargs rm -f

rm -f $(OBJS) *.bak tags TAGS

rm -fr *.*~

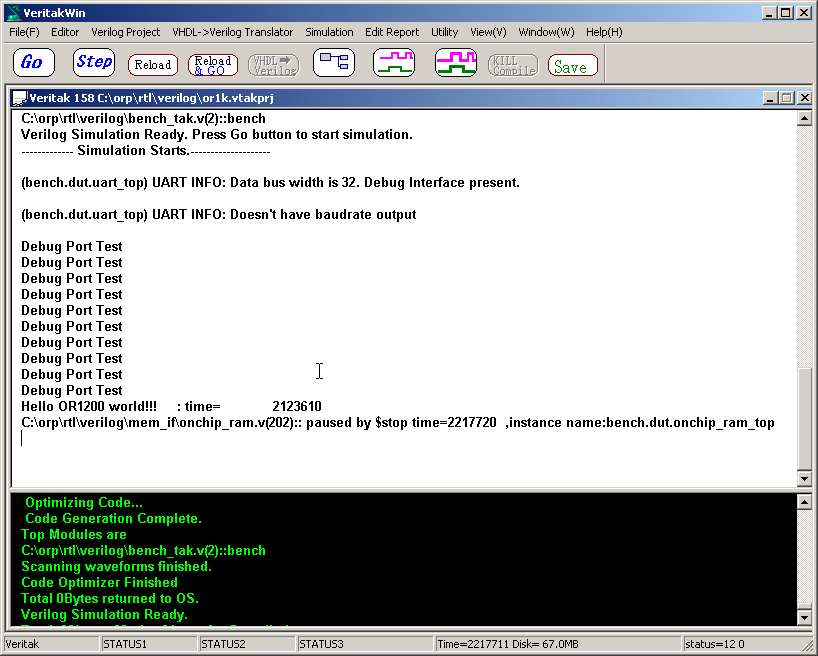

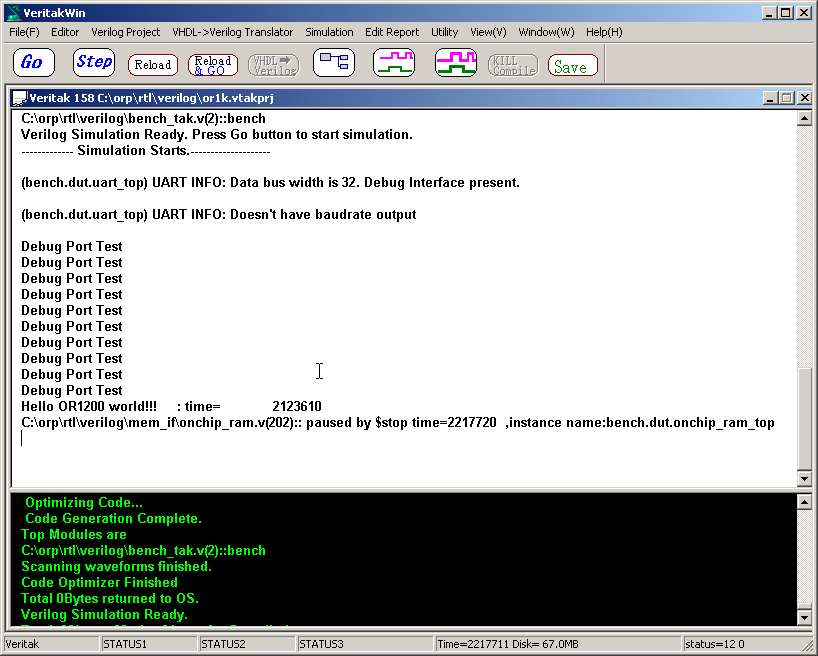

2. C source Execution

2.1 hello_uart

Here is a simple c source (main routine only)

char *str = "Hello OR1200 world!!!\n";

int main (void)

{

char *s;

int i;

for (i=0;i<10;i++) {

print("Debug Port Test\n");

}

uart_init ();

for (s = str; *s; s++)

uart_putc (*s);

print("$finish");

return 0;

}

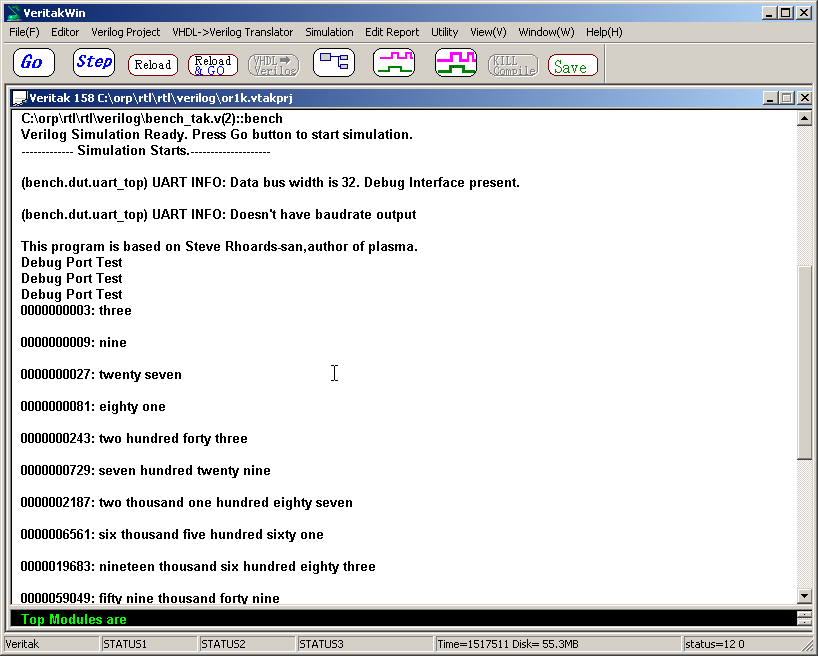

2.2 count

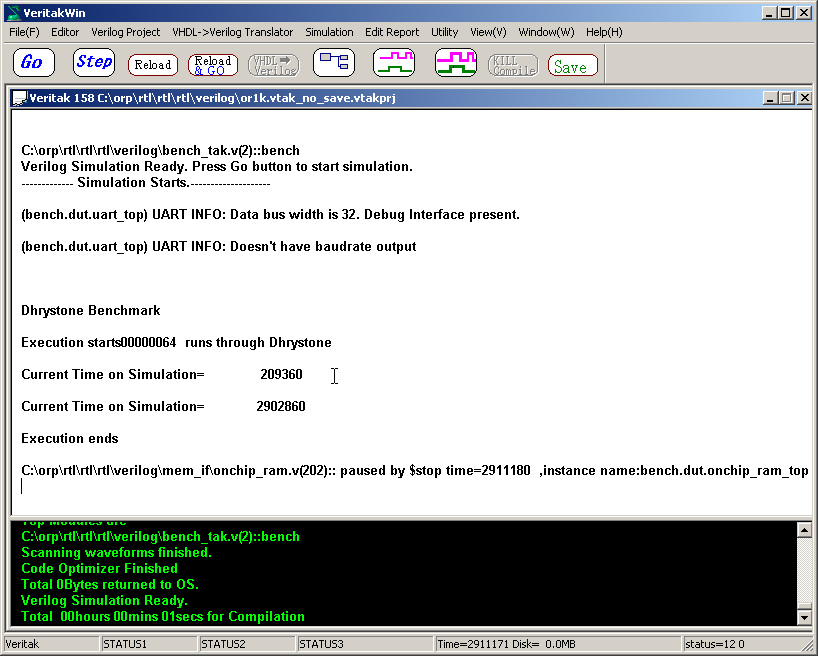

2.3 Dhrystone

Test Start 209360ns

Test Stop 2902860ns

(gcc -O3 is used. cache instruction 8KB/Data 8KB)

Since 100 cycles was done,

1 Cycle Time=(2902860-209360)/100=26935ns

This means

37100iterations/Sec at 50MHz Clock

=>742iterations/sec/MHz

(YACC is 59600iterations/Sec at 50MHz Clock =>1192iterations/sec/MHz

)

You can see the comparison report of LEON2, microblaze, and OPENRISC cpus.

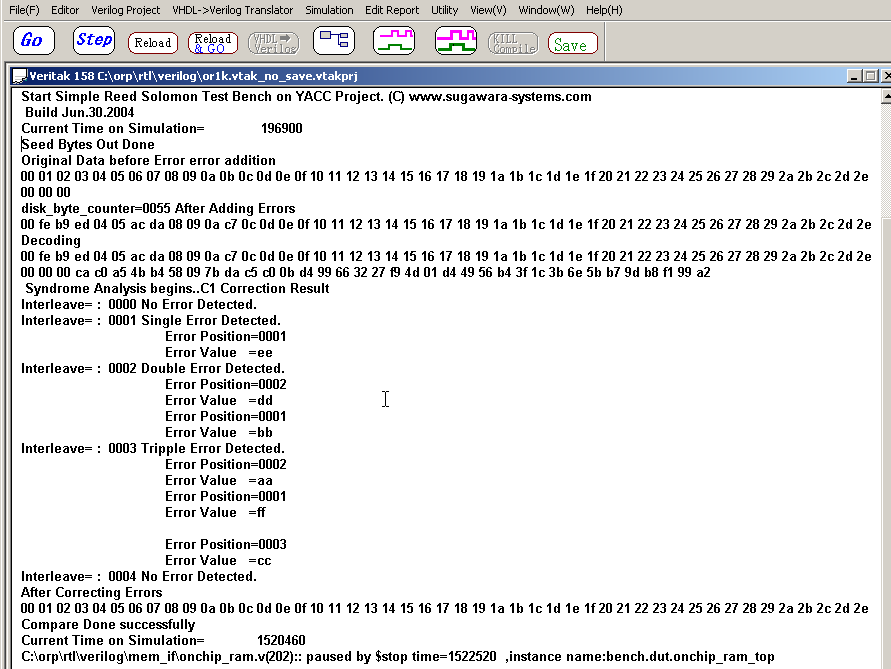

2.4 Reed Solomon

This bench takes about 1.3msec, which means 2times slower than YACC(650usec)

at 50MHz clock. You should understand YACC uses Dual PORT RAM, while Openrisc

uses One-Port RAM with cache mechanism and MMU. As you know this is not

fair comparison.